- 您现在的位置:买卖IC网 > Datasheet目录333 > ISL6261AEVAL1Z (Intersil)EVAL BOARD 1 FOR ISL6261A Datasheet资料下载

参数资料

| 型号: | ISL6261AEVAL1Z |

| 厂商: | Intersil |

| 文件页数: | 12/34页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD 1 FOR ISL6261A |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

�� �

�

�

�ISL6261A�

�Theory� of� Operation�

�The� ISL6261A� is� a� single-phase� regulator� implementing�

�Intel� ?� IMVP-6� ?� protocol� and� includes� an� integrated� gate�

�driver� for� reduced� system� cost� and� board� area.� The�

�VDD�

�ISL6261A� IMVP-6� ?� solution� provides� optimum� steady� state�

�and� transient� performance� for� microprocessor� core� voltage�

�regulation� applications� up� to� 25A.� Implementation� of� Diode�

�Emulation� Mode� (DEM)� operation� further� enhances� system�

�efficiency.�

�VR_ON�

�100μs�

�SOFT� &VO�

�20mV�

�10mV/μs�

�Vboot�

�13� x� T� s�

�The� heart� of� the� ISL6261A� is� the� patented� R� 3� Technology?,�

�Intersil’s� Robust� Ripple� Regulator� modulator.� The� R� 3� ?�

�modulator� combines� the� best� features� of� fixed� frequency� and�

�CLK_EN#�

�2mV/μs�

�hysteretic� PWM� controllers� while� eliminating� many� of� their�

�shortcomings.� The� ISL6261A� modulator� internally�

�synthesizes� an� analog� of� the� inductor� ripple� current� and�

�IMVP-VI� PGOOD�

�~7ms�

�uses� hysteretic� comparators� on� those� signals� to� establish�

�PWM� pulses.� Operating� on� the� large-amplitude� and� noise-�

�free� synthesized� signals� allows� the� ISL6261A� to� achieve�

�lower� output� ripple� and� lower� phase� jitter� than� either�

�conventional� hysteretic� or� fixed� frequency� PWM� controllers.�

�Unlike� conventional� hysteretic� converters,� the� ISL6261A� has�

�an� error� amplifier� that� allows� the� controller� to� maintain� 0.5%�

�voltage� regulation� accuracy� throughout� the� VID� range� from�

�0.75V� to� 1.5V.�

�The� hysteretic� window� voltage� is� with� respect� to� the� error�

�amplifier� output.� Therefore� the� load� current� transient� results�

�in� increased� switching� frequency,� which� gives� the� R� 3� ?�

�regulator� a� faster� response� than� conventional� fixed�

�frequency� PWM� regulators.�

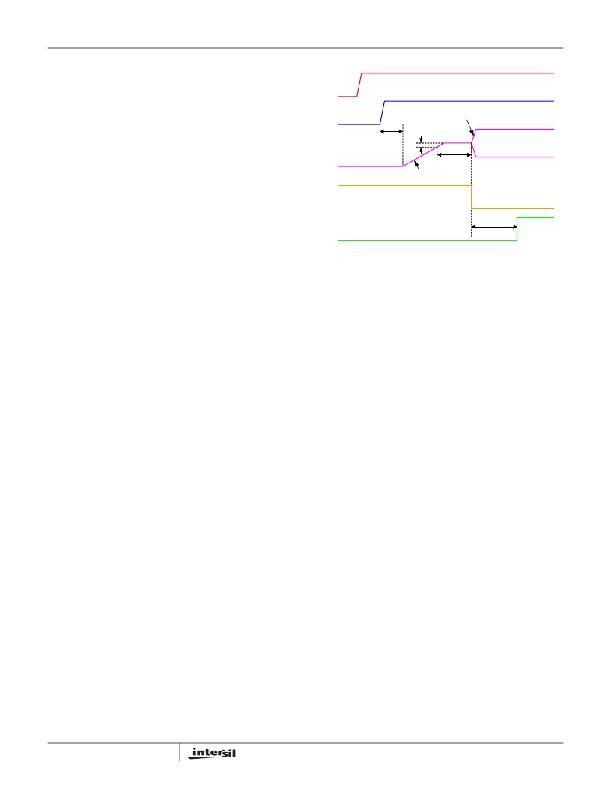

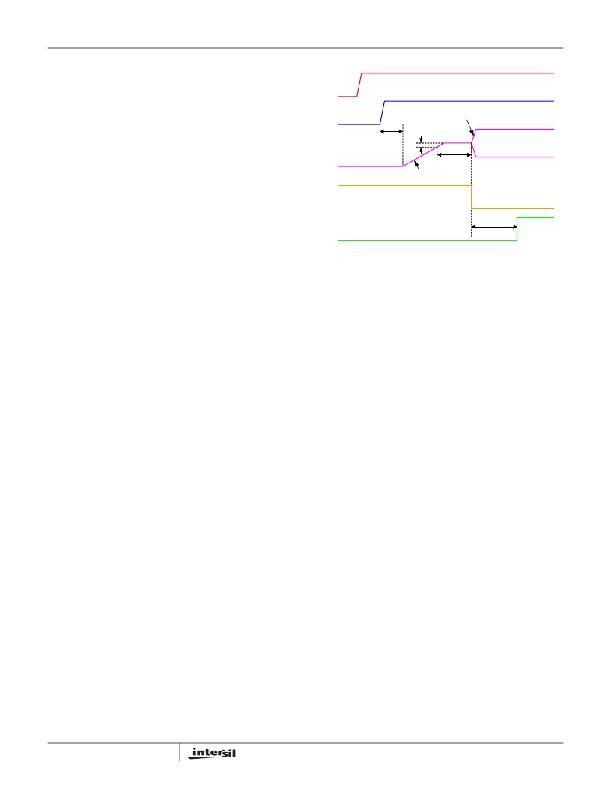

�Start-up� Timing�

�With� the� controller� ’s� VDD� pin� voltage� above� the� POR�

�threshold,� the� start-up� sequence� begins� when� VR_ON�

�exceeds� the� 3.3V� logic� HIGH� threshold.� In� approximately�

�100� μ� s,� SOFT� and� VO� start� ramping� to� the� boot� voltage� of�

�1.2V.� At� start-up,� the� regulator� always� operates� in�

�Continuous� Current� Mode� (CCM),� regardless� of� the� control�

�signals.� During� this� interval,� the� SOFT� cap� is� charged� by� a�

�41� μ� A� current� source.� If� the� SOFT� capacitor� is� 20nF,� the�

�SOFT� ramp� will� be� 2mV/μs� for� a� soft-start� time� of� 600μs.�

�Once� VO� is� within� 20mV� of� the� boot� voltage� the� ISL6261A�

�will� count� 13� clock� cycles,� then� pull� CLK_EN#� low,� and�

�charge/discharge� the� SOFT� cap� with� approximately� 200μA,�

�therefore� VO� slews� at� 10mV/μs� to� the� voltage� set� by� the� VID�

�pins.� In� approximately� 7ms,� PGOOD� is� asserted� HIGH.�

�Figure� 4� shows� typical� start-up� timing.�

�Static� Operation�

�After� the� start-up� sequence,� the� output� voltage� will� be�

�regulated� to� the� value� set� by� the� VID� inputs� per� Table� 1,�

�which� is� presented� in� the� lntel� ?� IMVP-6� ?� specification.� The�

�ISL6261A� regulates� the� output� voltage� with� ±0.5%� accuracy�

�over� the� range� of� 0.7V� to� 1.5V.�

�12�

�FIGURE� 4.� SOFT-START� WAVEFORMS� USING� A� 20nF� SOFT�

�CAPACITOR�

�A� true� differential� amplifier� remotely� senses� the� core� voltage�

�to� precisely� control� the� voltage� at� the� microprocessor� die.�

�VSEN� and� RTN� pins� are� the� inputs� to� the� differential�

�amplifier.�

�As� the� load� current� increases� from� zero,� the� output� voltage�

�droops� from� the� VID� value� proportionally� to� achieve� the�

�IMVP-6� ?� load� line.� The� ISL6261A� can� sense� the� inductor�

�current� through� the� intrinsic� series� resistance� of� the�

�inductors,� as� shown� in� Figure� 2,� or� through� a� precise� resistor�

�in� series� with� the� inductor,� as� shown� in� Figure� 3.� The�

�inductor� current� information� is� fed� to� the� VSUM� pin,� which� is�

�the� non-inverting� input� to� the� droop� amplifier.� The� DROOP�

�pin� is� the� output� of� the� droop� amplifier,� and� DROOP-VO�

�voltage� is� a� high-bandwidth� analog� representation� of� the�

�inductor� current.� This� voltage� is� used� as� an� input� to� a�

�differential� amplifier� to� achieve� the� IMVP-6� ?� load� line,� and�

�also� as� the� input� to� the� overcurrent� protection� circuit.�

�The� PMON� pin� is� the� power� monitor� output.� The� voltage�

�potential� on� this� pin� (V� PMON� )� is� given� by� V� PMON� =� 35x(V� SEN� -�

�V� RTN� )x(V� DROOP� -V� O� )� .� Since� V� SEN� -V� RTN� is� the� CPU� voltage�

�and� V� DROOP� -V� O� represents� the� inductor� current,� V� PMON� is�

�an� analog� voltage� indicating� the� power� consumed� by� the�

�CPU.� V� PMON� has� high� bandwidth� so� it� represents� the�

�instantaneous� power� including� the� pulsation� caused� inductor�

�current� switching� ripple.� The� maximum� available� V� PMON� is�

�approximately� 3V.�

�When� using� inductor� DCR� current� sensing,� an� NTC�

�thermistor� is� used� to� compensate� the� positive� temperature�

�coefficient� of� the� copper� winding� resistance� to� maintain� the�

�load-line� accuracy.�

�The� switching� frequency� of� the� ISL6261A� controller� is� set� by�

�the� resistor� R� FSET� between� pins� VW� and� COMP,� as� shown� in�

�Figures� 2� and� 3.�

�FN6354.3�

�November� 5,� 2009�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6261EVAL1Z | EVAL BOARD FOR ISL6261 1 QFN |

| ISL6271AEVAL1 | EVALUATION BOARD FOR ISL6271A |

| ISL62882CEVAL2Z | EVAL BOARD FOR ISL62882C |

| ISL62883CEVAL2Z | EVAL BOARD FOR ISL62883C |

| ISL62883EVAL2Z | EVALUATION BOARD FOR ISL62883 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6261AEVAL2Z | 功能描述:EVAL BOARD 2 FOR ISL6261A RoHS:是 类别:编程器,开发系统 >> 评估板 - 线性稳压器 (LDO) 系列:* 产品变化通告:1Q2012 Discontinuation 30/Mar/2012 设计资源:NCP590MNDPTAGEVB Gerber Files 标准包装:1 系列:- 每 IC 通道数:2 - 双 输出电压:1.8V,2.8V 电流 - 输出:300mA 输入电压:2.1 ~ 5.5 V 稳压器类型:正,固定式 工作温度:-40°C ~ 85°C 板类型:完全填充 已供物品:板 已用 IC / 零件:NCP590MNDP 其它名称:NCP590MNDPTAGEVB-NDNCP590MNDPTAGEVBOS |

| ISL6261AIRZ | 功能描述:DC/DC 开关控制器 ONE-PHS INT DC/DC BUCK CNTRLR IMVP-6 RoHS:否 制造商:Texas Instruments 输入电压:6 V to 100 V 开关频率: 输出电压:1.215 V to 80 V 输出电流:3.5 A 输出端数量:1 最大工作温度:+ 125 C 安装风格: 封装 / 箱体:CPAK |

| ISL6261AIRZ-T | 功能描述:DC/DC 开关控制器 ONE-PHS INT DC/DC BUCK CNTRLR IMVP-6 RoHS:否 制造商:Texas Instruments 输入电压:6 V to 100 V 开关频率: 输出电压:1.215 V to 80 V 输出电流:3.5 A 输出端数量:1 最大工作温度:+ 125 C 安装风格: 封装 / 箱体:CPAK |

| ISL6261CR7Z | 功能描述:IC CTRLR BUCK 1PHASE 48-VFQFN EP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

| ISL6261CR7Z-T | 功能描述:IC CTRLR BUCK 1PHASE 48-VFQFN-EP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - 专用型 系列:- 标准包装:43 系列:- 应用:控制器,Intel VR11 输入电压:5 V ~ 12 V 输出数:1 输出电压:0.5 V ~ 1.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-VFQFN 裸露焊盘 供应商设备封装:48-QFN(7x7) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。