参数资料

| 型号: | ISL6262CRZ-T |

| 厂商: | Intersil |

| 文件页数: | 15/27页 |

| 文件大小: | 0K |

| 描述: | IC CORE REG 2PHASE 48-QFN |

| 标准包装: | 4,000 |

| 应用: | 转换器,Intel IMVP-6 |

| 输入电压: | 5 V ~ 25 V |

| 输出数: | 1 |

| 输出电压: | 0.3 V ~ 1.5 V |

| 工作温度: | -10°C ~ 100°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘 |

| 供应商设备封装: | 48-QFN(7x7) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

�� �

�

�

�ISL6262�

�Theory� of� Operation�

�The� ISL6262� is� a� two-phase� regulator� implementing� Intel?�

�IMVP-6� protocol� and� includes� embedded� gate� drivers� for�

�V� DD�

�reduced� system� cost� and� board� area.� The� regulator� provides�

�optimum� steady-state� and� transient� performance� for�

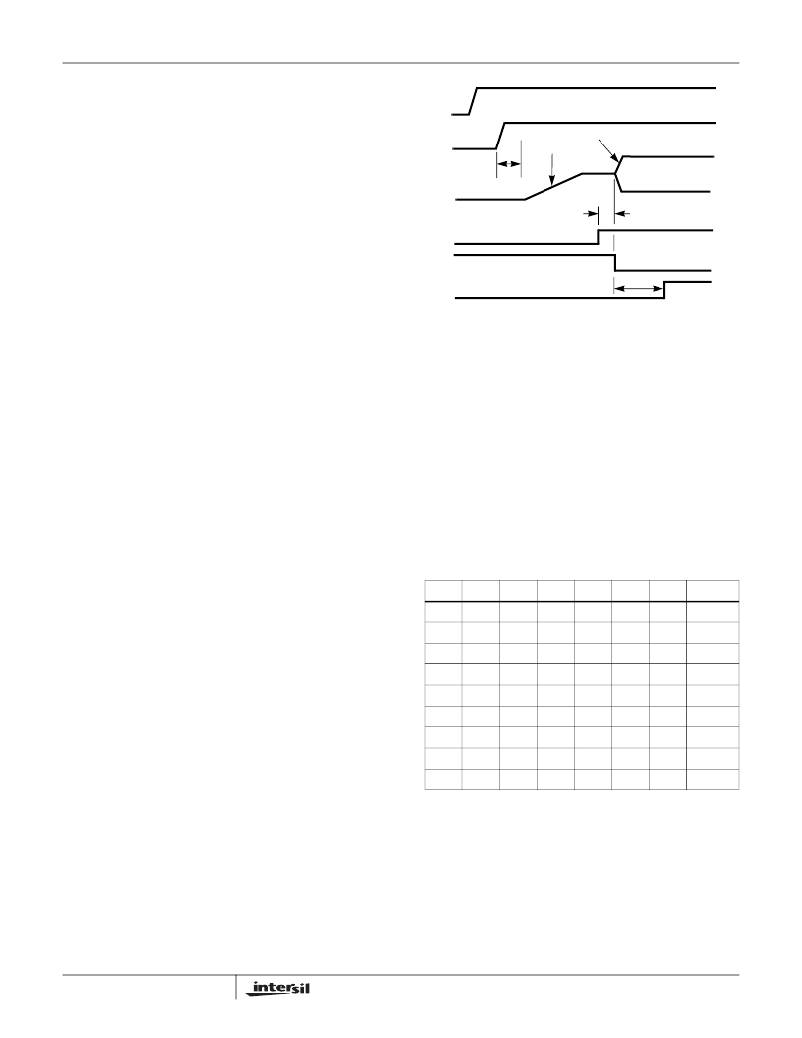

�VR_ON�

�10mV/μs�

�2mV/μs�

�microprocessor� core� applications� up� to� 50A.� System�

�efficiency� is� enhanced� by� idling� one� phase� at� low-current�

�and� implementing� automatic� DCM-mode� operation.�

�100μs�

�SOFT� &� VO�

�VBOOT�

�VID� COMMANDED�

�VOLTAGE�

�The� heart� of� the� ISL6262� is� R� 3� Technology?,� Intersil’s�

�Robust� Ripple� Regulator� modulator.� The� R� 3� modulator�

�combines� the� best� features� of� fixed� frequency� PWM� and�

�hysteretic� PWM� while� eliminating� many� of� their�

�PGD_IN�

�CLK_EN#�

�20μs�

�shortcomings.� The� ISL6262� modulator� internally� synthesizes�

�an� analog� of� the� inductor� ripple� current� and� uses� hysteretic�

�IMVP-6� PGOOD�

�6.8ms�

�comparators� on� those� signals� to� establish� PWM� pulse�

�widths.� Operating� on� these� large-amplitude,� noise-free�

�synthesized� signals� allows� the� ISL6262� to� achieve� lower�

�output� ripple� and� lower� phase� jitter� than� either� conventional�

�hysteretic� or� fixed� frequency� PWM� controllers.� Unlike�

�conventional� hysteretic� converters,� the� ISL6262� has� an� error�

�amplifier� that� allows� the� controller� to� maintain� a� 0.5%� voltage�

�regulation� accuracy� throughout� the� VID� range� from� 0.75V� to�

�1.5V.�

�The� hysteresis� window� voltage� is� relative� to� the� error�

�amplifier� output� such� that� load� current� transients� results� in�

�increased� switching� frequency,� which� gives� the� R� 3� regulator�

�a� faster� response� than� conventional� fixed� frequency� PWM�

�controllers.� Transient� load� current� is� inherently� shared�

�between� active� phases� due� to� the� use� of� a� common�

�hysteretic� window� voltage.� Individual� average� phase�

�voltages� are� monitored� and� controlled� to� equally� share� the�

�FIGURE� 28.� SOFT-START� WAVEFORMS� USING� A� 20nF� SOFT�

�CAPACITOR�

�PGD_IN� Latch�

�It� should� be� noted� that� PGD_IN� going� low� will� cause� the�

�converter� to� latch� off.� This� state� will� be� cleared� when� VR_ON�

�is� toggled.� This� feature� allows� the� converter� to� respond� to�

�other� system� voltage� outages� immediately.�

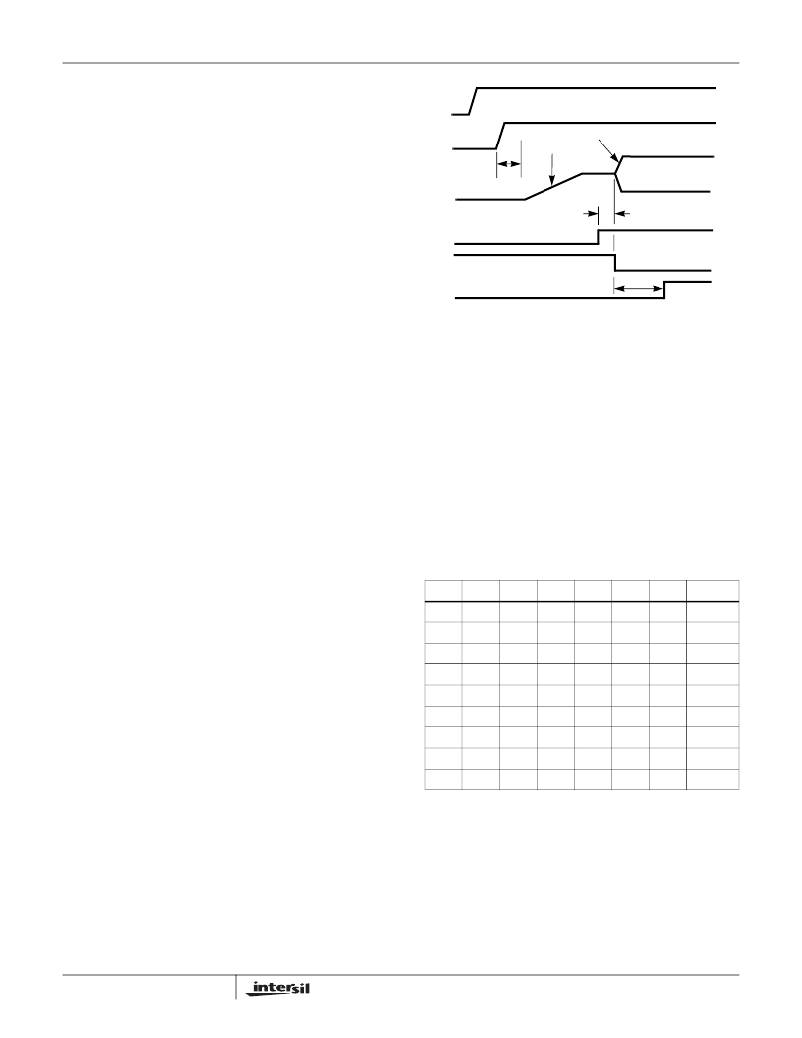

�Static� Operation�

�After� the� start� sequence,� the� output� voltage� will� be� regulated�

�to� the� value� set� by� the� VID� inputs� per� Table� 1.� The� entire� VID�

�table� is� presented� in� the� intel� IMVP-6� specification.� The�

�ISL6262� will� control� the� no-load� output� voltage� to� an�

�accuracy� of� ±0.5%� over� the� range� of� 0.75V� to� 1.5V.�

�TABLE� 1.� TRUNCATED� VID� TABLE� FOR� INTEL� IMVP-6�

�SPECIFICATION�

�static� current� among� the� active� phases.�

�VID6�

�VID5�

�VID4�

�VID3�

�VID2�

�VID1�

�VID0� VOUT� (V)�

�Start-Up� Timing�

�With� the� controller's� +5V� VDD� voltage� above� the� POR�

�threshold,� the� start-up� sequence� begins� when� VR_ON�

�exceeds� the� 3.3V� logic� HIGH� threshold.� Approximately�

�100μs� later,� SOFT� and� VOUT� begin� ramping� to� the� boot�

�voltage� of� 1.2V.� At� start-up,� the� regulator� always� operates� in�

�a� 2-phase� CCM� mode,� regardless� of� control� signal� assertion�

�levels.� During� this� internal,� the� SOFT� cap� is� charged� by�

�41μA� current� source.� If� the� SOFT� capacitor� is� selected� to� be�

�20nF,� the� SOFT� ramp� will� be� at� 2mV/s� for� a� soft-start� time� of�

�600μs.� Once� VOUT� is� within� 10%� of� the� boot� voltage�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�1�

�1�

�0�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�0�

�1�

�0�

�0�

�0�

�0�

�1�

�0�

�1�

�0�

�1�

�0�

�0�

�1�

�0�

�1�

�1�

�0�

�0�

�1�

�0�

�0�

�0�

�0�

�0�

�0�

�1�

�0�

�1�

�0�

�1�

�1�

�1�

�0�

�1�

�1�

�0�

�1�

�1.5000�

�1.4875�

�1.4375�

�1.2875�

�1.15�

�0.8375�

�0.7625�

�0.3000�

�0.0000�

�and� PGD_IN� is� HIGH� for� six� PWM� cycles� (20μs� for�

�frequency� =� 300kHz),� then� CLK_EN#� is� pulled� LOW� and� the�

�SOFT� cap� is� charged/discharged� by� approximate� 200μA.�

�Therefore,� VOUT� slews� at� +10mV/s� to� the� voltage� set� by� the�

�VID� pins.� Approximately� 7ms� later,� PGOOD� is� asserted�

�HIGH.� Typical� start-up� timing� is� shown� in� Figure� 28.�

�15�

�A� fully-differential� amplifier� implements� core� voltage� sensing�

�for� precise� voltage� control� at� the� microprocessor� die.� The�

�inputs� to� the� amplifier� are� the� VSEN� and� RTN� pins.�

�As� the� load� current� increases� from� zero,� the� output� voltage�

�will� droop� from� the� VID� table� value� by� an� amount�

�proportional� to� current� to� achieve� the� IMVP-6� load� line.� The�

�ISL6262� provides� for� current� to� be� measured� using� either�

�resistors� in� series� with� the� channel� inductors� as� shown� in� the�

�application� circuit� of� Figure� 27,� or� using� the� intrinsic� series�

�FN9199.2�

�May� 15,� 2006�

�相关PDF资料 |

PDF描述 |

|---|---|

| X40030S14I-CT1 | IC VOLTAGE MONITOR TRPL 14-SOIC |

| ASC25DREN-S13 | CONN EDGECARD 50POS .100 EXTEND |

| X40030S14I-C | IC VOLTAGE MONITOR TRPL 14-SOIC |

| X40030S14I-BT1 | IC VOLTAGE MONITOR TRPL 14-SOIC |

| ISL6336AIRZ | IC CTRLR PWM 6PHASE BUCK 48-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6262CRZ-TK | 功能描述:直流/直流开关调节器 TWO-PHS DC/DC BUCK CNTRLR IMVP-6 4 8LD RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| ISL6262CRZ-TR5242 | 制造商:Intersil Corporation 功能描述:53350B01 MASK ONLY AND DOT ON BRAND - Tape and Reel |

| ISL6262IRZ | 功能描述:直流/直流开关调节器 TWO-PHS DC/DC BUCK CNTRLR IMVP-6 4 8LD RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| ISL6262IRZ-T | 功能描述:直流/直流开关调节器 TWO-PHS DC/DC BUCK CNTRLR IMVP-6 4 8LD RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| ISL6263 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5-Bit VID Single-Phase Voltage Regulator for IMVP-6 Santa Rosa GPU Core |

发布紧急采购,3分钟左右您将得到回复。