- 您现在的位置:买卖IC网 > PDF目录16776 > ISL6271ACRZ-T (Intersil)IC PMIC XSCALE REG 20-QFN PDF资料下载

参数资料

| 型号: | ISL6271ACRZ-T |

| 厂商: | Intersil |

| 文件页数: | 11/16页 |

| 文件大小: | 0K |

| 描述: | IC PMIC XSCALE REG 20-QFN |

| 标准包装: | 1 |

| 应用: | 处理器 |

| 电流 - 电源: | 380µA |

| 电源电压: | 2.76 V ~ 5.5 V |

| 工作温度: | -25°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-VFQFN 裸露焊盘 |

| 供应商设备封装: | 20-QFN 裸露焊盘(4x4) |

| 包装: | 标准包装 |

| 产品目录页面: | 1248 (CN2011-ZH PDF) |

| 其它名称: | ISL6271ACRZ-TDKR |

�� �

�

�

�ISL6271A�

�I� 2� C� SEND� BYTE� PROTOCOL�

�SLEW�

�VOLTAGE�

�SET�

�Application� Guidelines�

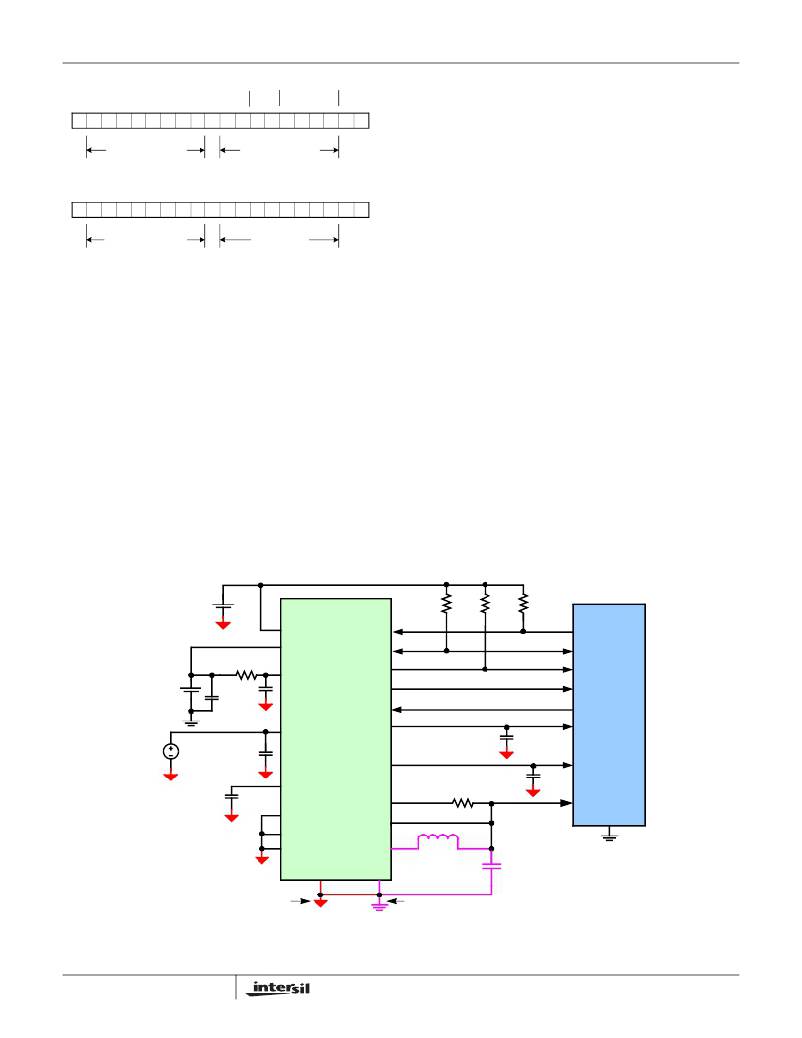

�Every� effort� should� be� made� to� place� the� ISL6271A� as� close�

�S�

�0� 0� 0� 1� 1� 0� 0� 0� 0� X�

�X� D5� D4� D3� D2� D1� D0� 0�

�P�

�as� possible� to� the� processor,� with� the� orientation� favoring� the�

�START� A6� A5� A4� A3� A2� A1� A0� W� A�

�SLAVE� ADDRESS�

�I� 2� C RECEIVE BYTE PROTCOL�

�COMMAND� BYTE�

�A� STOP�

�shortest� voltage� routing.� The� regulator� input� capacitors�

�should� be� located� close� to� their� respective� input� pins.�

�All� output� capacitors� should� be� kept� close� to� their� respective�

�output� pins� with� the� ground� pins� connected� immediately� to�

�S�

�0� 0� 0� 1� 1� 0� 0�

�1� 0� D7� D6� D5� D4� D3� D2� D1� D0� 1�

�P�

�the� ground� plane.� Care� should� be� taken� to� avoid� routing�

�START� A6� A5� A4� A3� A2� A1� A0� W� A�

�SLAVE� ADDRESS�

�DATA� BYTE�

�A� STOP�

�sensitive,� high� impedance� signals� near� the� PHASE� pin� on�

�the� controller,� and� the� attendant� PCB� traces.�

�To� minimize� switching� noise,� it� is� important� to� keep� the� loop�

�FIGURE� 18.� INTERFACE� BIT� DEFINITION� AND� PROTOCOL�

�VID� and� Slew� Rate� Program� Register�

�In� a� typical� XScale� configuration,� the� processor� ’s� “Power�

�Manager”� will� issue� the� voltage� and� slew� rate� commands� to�

�the� ISL6271A� over� its� PWR_� I� 2� C� bus� after� the� ISL6271A�

�acknowledges� its� address.� The� data� byte� is� composed� of� two�

�pieces� of� ‘set’� information:� The� prescribed� voltage� level�

�embedded� in� bits� D0-D3,� and� the� prescribed� transition� slew�

�rate� (from� the� previous� voltage� to� the� target� voltage)�

�embedded� in� bits� D4-D5.� Each� set� of� bits� is� transmitted� MSB�

�first.� This� protocol� is� depicted� in� Figure� 18.�

�area� associated� with� the� phase� node� and� output� filter� as�

�short� as� possible.� It� is� also� important� that� the� input� voltage�

�decoupling� capacitor� C7� be� located� as� close� to� the� PVCC�

�pin� as� possible� and� that� it� has� a� low� impedance� return� path�

�to� the� PGND� pin.� In� general� a� good� approach� to� layout� is� to�

�consider� how� switching� current� flows� in� a� circuit,� and� to�

�minimize� the� loop� area� associated� with� this� current.� In� the�

�case� of� the� switching� regulator,� current� flows� from� C7�

�through� the� internal� upper� P-MOSFET,� to� the� load� through�

�the� output� filter� and� back� to� the� PGND� pin.� To� maximize� the�

�effectiveness� of� any� decoupling� capacitor,� minimize� the�

�parasitic� inductance� between� the� capacitor� and� the� circuit� it�

�is� decoupling.� Notice� that� Figure� 19� illustrates� the� SIGNAL�

�ground� with� RED� highlighting.� All� components� associated�

�with� these� terminals� should� be� tied� together� first.� Be� sure� to�

�make� only� one� connection� between� this� net� and� the� PGND�

�pin� to� avoid� ground� loops� and� noise� injection� points� into�

�sensitive� analog� circuitry.�

�BBAT� ≤� VCC�

�COIN� CELL�

�BACK-UP�

�Li-ion�

�4.2V�

�TO�

�2.60V�

�R7,� 10� ?�

�C3�

�0.1μF�

�C7�

�10μF�

�BBAT�

�PVCC�

�VCC�

�ISL6271A�

�SCL/VID0�

�SDA/VID1�

�PGOOD�

�BFLT#�

�EN�

�5k� ?�

�5k� ?�

�5k� ?�

�XScale� μP�

�PWR_I2C�

�FAULT�

�REG.� EN�

�1.8V�

�OR� 2.5V�

�C4�

�10nF�

�X7R�

�C2�

�2.2μF�

�LVCC�

�SOFT�

�VSRAM�

�VPLL�

�FB�

�C8�

�2.2μF�

�X5R�

�Rcomp,� 50K�

�C5�

�2.2μF�

�X5R�

�VCC_SRAM�

�VCC_PLL�

�VCC_CORE�

�VIDEN�

�VID2�

�VOUT�

�VID3�

�GND�

�PHASE�

�PGND�

�L1�

�4.7μH�

�C6�

�10μF�

�X5R�

�Single� point� connection�

�between� PGND� and� GND� pins�

�Power� ground.� Minimize� the� loop� area� associated�

�with� L1,� C6� and� the� PHASE� and� PGND� pins.�

�FIGURE� 19.� TYPICAL� APPLICATION� CIRCUIT�

�11�

�FN9171.1�

�相关PDF资料 |

PDF描述 |

|---|---|

| RBC10DRTN-S734 | CONN EDGECARD 20POS DIP .100 SLD |

| H0PPS-2018G | DIP CABLE - HDP20S/AE20G/HDP20S |

| B78108S1475J | CHOKE RF 4700UH 55MA AXIAL |

| 381A303-51-0 | BOOT MOLDED |

| ECM24DSXH | CONN EDGECARD 48POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6271AEVAL1 | 功能描述:EVALUATION BOARD FOR ISL6271A RoHS:否 类别:编程器,开发系统 >> 评估板 - DC/DC 与 AC/DC(离线)SMPS 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:True Shutdown™ 主要目的:DC/DC,步升 输出及类型:1,非隔离 功率 - 输出:- 输出电压:- 电流 - 输出:1A 输入电压:2.5 V ~ 5.5 V 稳压器拓扑结构:升压 频率 - 开关:3MHz 板类型:完全填充 已供物品:板 已用 IC / 零件:MAX8969 |

| ISL6271CR | 制造商:Rochester Electronics LLC 功能描述:PLL & SRAM REGULATOR FOR INTEL PROCESSORS - Bulk 制造商:Intersil Corporation 功能描述: |

| ISL6271EVAL1 | 制造商:Intersil Corporation 功能描述:ISL6271, PLL & SRAM REGULATOR FOR INTEL PROCESSORS EVALUATIO - Bulk |

| ISL6273 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:1.2A Low Quiescent Current 1.5MHz High Efficiency Synchronous Buck Regulator |

| ISL6273EVAL1 | 功能描述:EVAL BOARD 1 FOR ISL6273 RoHS:否 类别:编程器,开发系统 >> 评估板 - 线性稳压器 (LDO) 系列:* 产品变化通告:1Q2012 Discontinuation 30/Mar/2012 设计资源:NCP590MNDPTAGEVB Gerber Files 标准包装:1 系列:- 每 IC 通道数:2 - 双 输出电压:1.8V,2.8V 电流 - 输出:300mA 输入电压:2.1 ~ 5.5 V 稳压器类型:正,固定式 工作温度:-40°C ~ 85°C 板类型:完全填充 已供物品:板 已用 IC / 零件:NCP590MNDP 其它名称:NCP590MNDPTAGEVB-NDNCP590MNDPTAGEVBOS |

发布紧急采购,3分钟左右您将得到回复。