- 您现在的位置:买卖IC网 > PDF目录15161 > ISL6326CRZ (Intersil)IC REG CTRLR BUCK PWM VM 40-QFN PDF资料下载

参数资料

| 型号: | ISL6326CRZ |

| 厂商: | Intersil |

| 文件页数: | 19/30页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM VM 40-QFN |

| 标准包装: | 50 |

| PWM 型: | 电压模式 |

| 输出数: | 1 |

| 频率 - 最大: | 275kHz |

| 占空比: | 25% |

| 电源电压: | 4.75 V ~ 5.25 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 40-VFQFN 裸露焊盘 |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

�� �

�

�

�ISL6326�

�Dynamic� VID�

�Modern� microprocessors� need� to� make� changes� to� their�

�core� voltage� as� part� of� normal� operation.� They� direct� the�

�core� voltage� regulator� to� do� this� by� making� changes� to� the�

�VID� inputs� during� regulator� operation.� The� power�

�family� of� Intersil� MOSFET� drivers,� which� require� 12V�

�bias.�

�3.� The� voltage� on� EN_VTT� must� be� higher� than� 0.875V� to�

�enable� the� controller.� This� pin� is� typically� connected� to� the�

�output� of� VTT� VR.�

�management� solution� is� required� to� monitor� the� DAC� inputs�

�and� respond� to� on-the-fly� VID� changes� in� a� controlled�

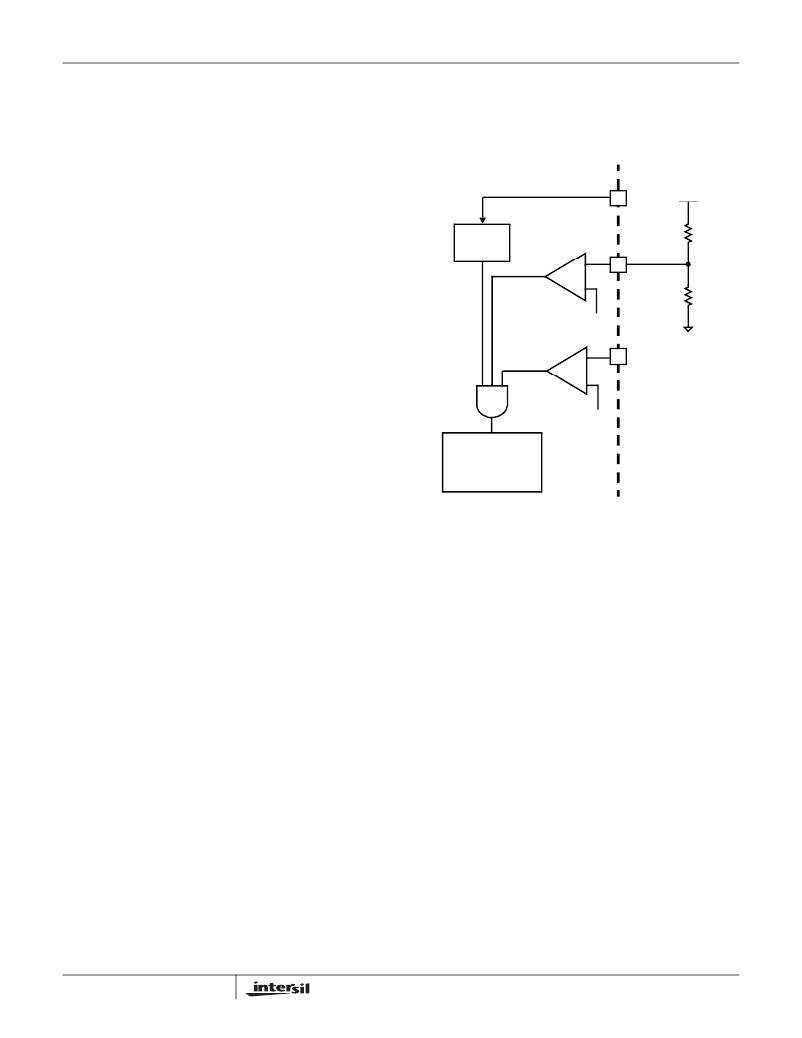

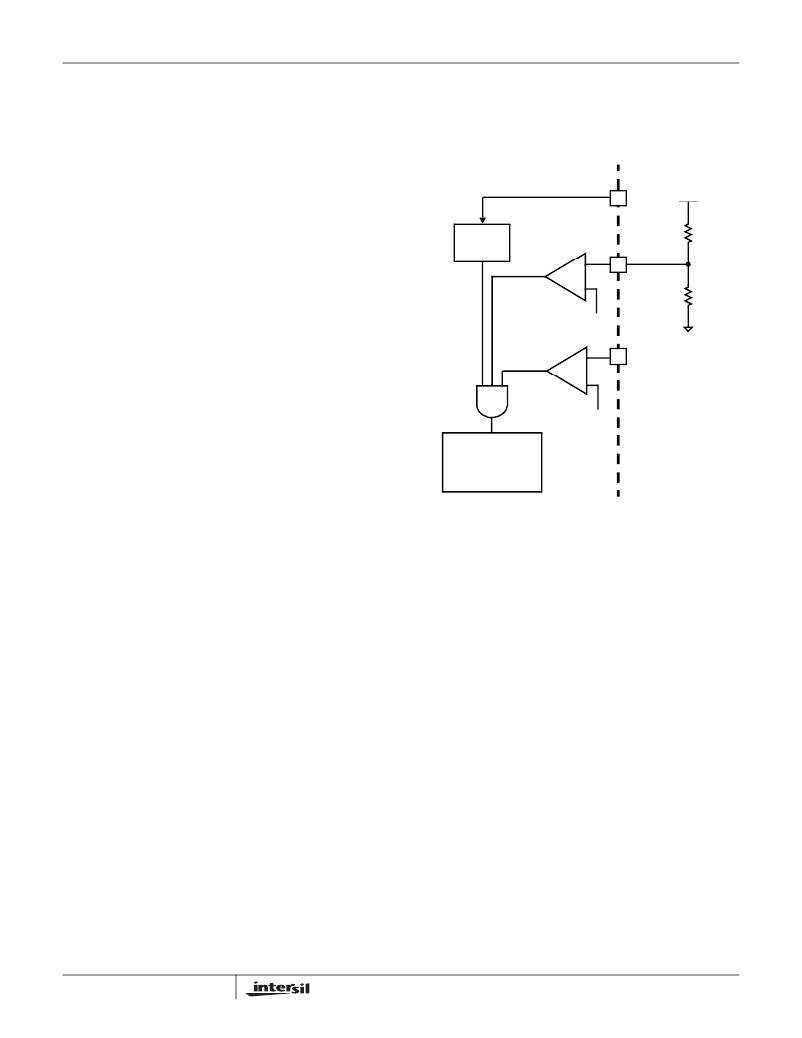

�ISL6326� INTERNAL� CIRCUIT�

�EXTERNAL� CIRCUIT�

�manner.� Supervising� the� safe� output� voltage� transition� within�

�the� DAC� range� of� the� processor� without� discontinuity� or�

�VCC�

�+� 12� V�

�disruption� is� a� necessary� function� of� the� core� voltage�

�regulator.�

�In� order� to� ensure� the� smooth� transition� of� output� voltage�

�during� VID� change,� a� VID� step� change� smoothing� network,�

�composed� of� R� REF� and� C� REF� ,� as� shown� in� Figure� 6,� can� be�

�used.� The� selection� of� R� REF� is� based� on� the� desired� offset�

�POR�

�CIRCUIT�

�ENABLE�

�COMPARATOR�

�+�

�-�

�0.875V�

�10k� Ω�

�EN_PWR�

�910� Ω�

���on� the� time� duration� for� 1-bit� VID� change� and� the� allowable�

�delay� time.�

�Assuming� the� microprocessor� controls� the� VID� change� at�

�1-bit� every� t� VID� ,� the� relationship� between� the� time� constant�

�of� R� REF� and� C� REF� network� and� t� VID� is� given� by� Equation� 13:�

�+�

�-�

�0.875V�

�EN_VTT�

�C� REF� R� REF� =� T� VID�

�(EQ.� 13)�

�SOFT-START�

�AND�

�FAULT� LOGIC�

�Operation� Initialization�

�Prior� to� converter� initialization,� proper� conditions� must� exist�

�on� the� enable� inputs� and� VCC.� When� the� conditions� are� met,�

�the� controller� begins� soft-start.� Once� the� output� voltage� is�

�within� the� proper� window� of� operation,� VR_RDY� asserts�

�logic� high.�

�Enable� and� Disable�

�While� in� shutdown� mode,� the� PWM� outputs� are� held� in� a�

�high-impedance� state� to� assure� the� drivers� remain� off.� The�

�following� input� conditions� must� be� met� before� the� ISL6326� is�

�released� from� shutdown� mode.�

�1.� The� bias� voltage� applied� at� VCC� must� reach� the� internal�

�power-on� reset� (POR)� rising� threshold.� Once� this�

�threshold� is� reached,� proper� operation� of� all� aspects� of�

�the� ISL6326� is� guaranteed.� Hysteresis� between� the� rising�

�and� falling� thresholds� assure� that� once� enabled,� the�

�ISL6326� will� not� inadvertently� turn� off� unless� the� bias�

�voltage� drops� substantially� (see� “Electrical�

�Specifications”� on� page� 6).�

�2.� The� ISL6326� features� an� enable� input� (EN_PWR)� for�

�power� sequencing� between� the� controller� bias� voltage�

�and� another� voltage� rail.� The� enable� comparator� holds�

�the� ISL6326� in� shutdown� until� the� voltage� at� EN_PWR�

�rises� above� 0.875V.� The� enable� comparator� has� about�

�FIGURE� 7.� POWER� SEQUENCING� USING� THRESHOLD-�

�SENSITIVE� ENABLE� (EN)� FUNCTION�

�When� all� conditions� are� satisfied,� ISL6326� begins� the�

�soft-start� and� ramps� the� output� voltage� to� 1.1V� first.� After�

�remaining� at� 1.1V� for� some� time,� ISL6326� reads� the� VID�

�code� at� VID� input� pins.� If� the� VID� code� is� valid,� ISL6326� will�

�regulate� the� output� to� the� final� VID� setting.� If� the� VID� code� is�

�OFF� code,� ISL6326� will� shutdown,� and� cycling� VCC,�

�EN_PWR� or� EN_VTT� is� needed� to� restart.�

�Soft-Start�

�ISL6326� based� VR� has� 4� periods� during� soft-start� as� shown�

�in� Figure� 8.� After� VCC,� EN_VTT� and� EN_PWR� reach� their�

�POR/enable� thresholds,� The� controller� will� have� fixed� delay�

�period� t� d1� .� After� this� delay� period,� the� VR� will� begin� first�

�soft-start� ramp� until� the� output� voltage� reaches� 1.1V� V� BOOT�

�voltage.� Then,� the� controller� will� regulate� the� VR� voltage� at�

�1.1V� for� another� fixed� period� t� d3� .� At� the� end� of� t� d3� period,�

�ISL6326� reads� the� VID� signals.� If� the� VID� code� is� valid,�

�ISL6326� will� initiate� the� second� soft-start� ramp� until� the�

�voltage� reaches� the� VID� voltage� minus� offset� voltage.�

�The� soft-start� time� is� the� sum� of� the� 4� periods,� as� shown� in�

�Equation� 14:�

�130mV� of� hysteresis� to� prevent� bounce.� It� is� important�

�that� the� driver� ICs� reach� their� POR� level� before� the�

�ISL6326� becomes� enabled.� The� schematic� in� Figure� 7�

�demonstrates� sequencing� the� ISL6326� with� the� ISL66xx�

�19�

�t� SS� =� t� d1� +� t� d2� +� t� d3� +� t� d4�

�(EQ.� 14)�

�FN9262.1�

�May� 5,� 2008�

�相关PDF资料 |

PDF描述 |

|---|---|

| EBM12DRMN-S273 | CONN EDGECARD 24POS .156 WW |

| EBM12DRMD-S273 | CONN EDGECARD 24POS .156 WW |

| ISL8126CRZ | IC REG CTRLR BUCK PWM VM 32-QFN |

| GEM43DSES-S243 | CONN EDGECARD 86POS .156 EYELET |

| UPJ1A682MHD6 | CAP ALUM 6800UF 10V 20% RADIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6326CRZ-T | 功能描述:电流型 PWM 控制器 W/ANNEAL 4-PHS VR11 CNTRLR COM RoHS:否 制造商:Texas Instruments 开关频率:27 KHz 上升时间: 下降时间: 工作电源电压:6 V to 15 V 工作电源电流:1.5 mA 输出端数量:1 最大工作温度:+ 105 C 安装风格:SMD/SMT 封装 / 箱体:TSSOP-14 |

| ISL6326CRZ-TR5453 | 制造商:Intersil Corporation 功能描述:STD. ISL6326CRZ-T W/GOLD BOND WIRE ONLY - Tape and Reel |

| ISL6326IRZ | 功能描述:电流型 PWM 控制器 W/ANNEAL 4-PHS VR11 CNTRLR IND RoHS:否 制造商:Texas Instruments 开关频率:27 KHz 上升时间: 下降时间: 工作电源电压:6 V to 15 V 工作电源电流:1.5 mA 输出端数量:1 最大工作温度:+ 105 C 安装风格:SMD/SMT 封装 / 箱体:TSSOP-14 |

| ISL6326IRZ-T | 功能描述:电流型 PWM 控制器 W/ANNEAL 4-PHS VR11 CNTRLR IND RoHS:否 制造商:Texas Instruments 开关频率:27 KHz 上升时间: 下降时间: 工作电源电压:6 V to 15 V 工作电源电流:1.5 mA 输出端数量:1 最大工作温度:+ 105 C 安装风格:SMD/SMT 封装 / 箱体:TSSOP-14 |

| ISL6327ACRZ | 功能描述:IC REG CTRLR BUCK PWM 48-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。