参数资料

| 型号: | ISL6740AIVZA |

| 厂商: | Intersil |

| 文件页数: | 12/14页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR PWM VM 16-TSSOP |

| 标准包装: | 960 |

| PWM 型: | 电压模式 |

| 输出数: | 1 |

| 频率 - 最大: | 2MHz |

| 占空比: | 100% |

| 电源电压: | 9 V ~ 16 V |

| 降压: | 无 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 105°C |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 包装: | 管件 |

�� �

�

�

�ISL6740A�

�SS�

�4.5� V�

�1�

�16�

�4.25� V�

�0.27� V�

�2�

�3�

�VREF� 15�

�14�

�0.6� V� OC�

�CS�

�OUTA�

�4�

�5�

�6�

�7�

�ISL6740A�

�13�

�12�

�11�

�10�

�R�

�OUTB�

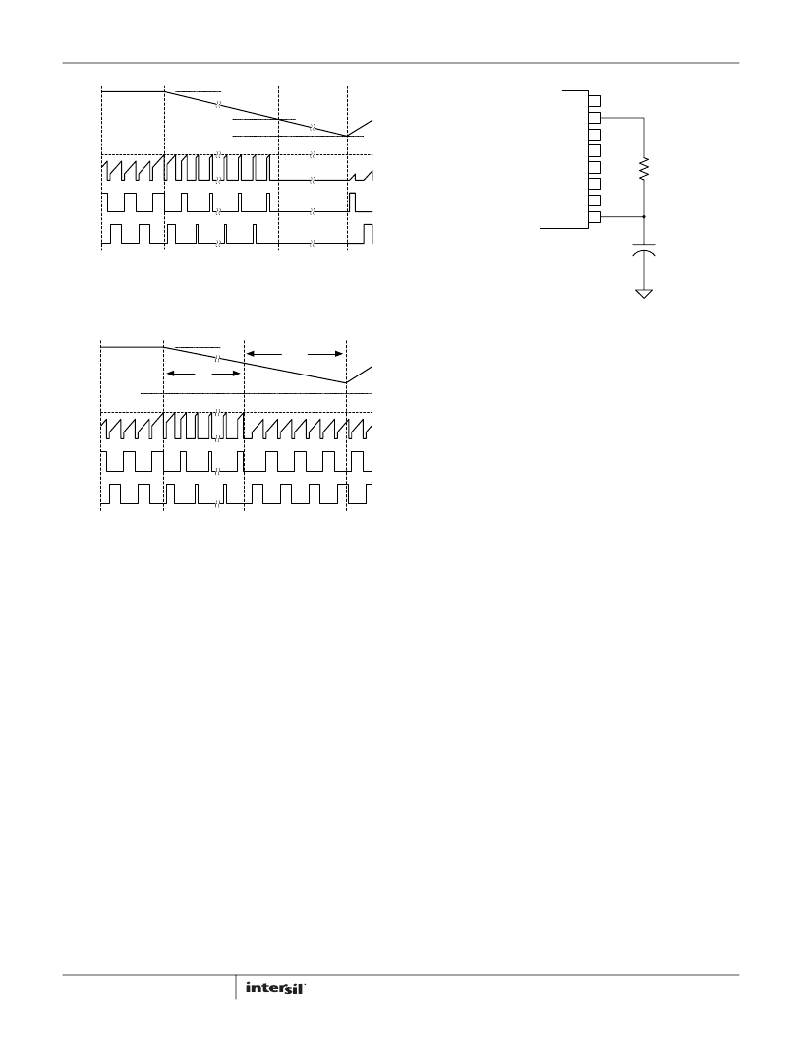

�FIGURE� 8.� OC� SHUTDOWN� BEHAVIOR�

�Figure� 8� portrays� the� typical� delayed� overcurrent� shutdown�

�8�

�SS� 9�

�C� SS�

�behavior.� Once� SS� has� discharged� to� 4.25V,� the� outputs� are�

�disabled� and� remain� that� way� until� SS� has� discharged� to�

�0.27V,� and� then� a� new� SS� cycle� begins.�

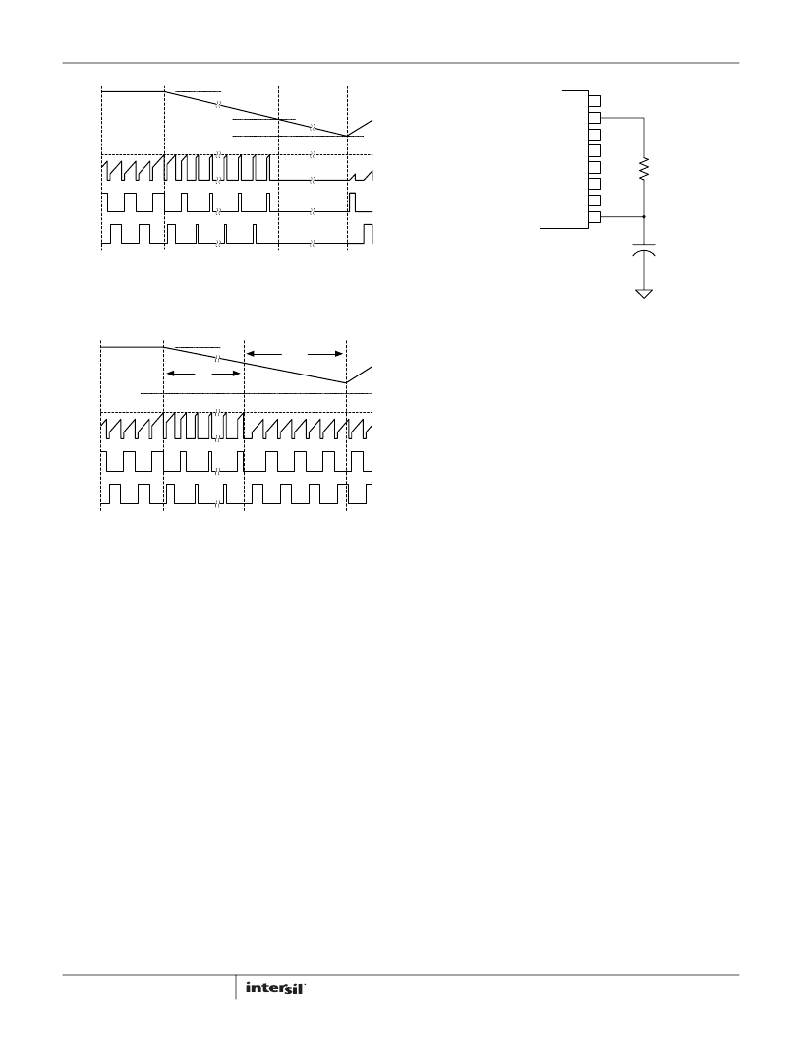

�FIGURE� 10.� MODIFYING� OC� SHUTDOWN� TIMING�

�Short� Circuit� Operation�

�SS�

�0.6� V� OC�

�CS�

�4.25� V�

�OC�

�4.5� V�

�50� μ� S�

�If� the� output� current� increases� beyond� the� overcurrent�

�threshold,� peak� current� limit� will� reduce� the� duty� cycle.� As� the�

�load� current� continues� to� increase,� the� duty� cycle� continues� to�

�decrease.� A� short� circuit� event� is� defined� as� the� simultaneous�

�occurrence� of� current� limit� and� a� reduced� duty� cycle.�

�The� degree� of� reduced� duty� cycle� that� defines� a� short� circuit�

�condition� is� user� adjustable� using� the� SCSET� input.� A� resistor�

�OUTA�

�OUTB�

�divider� between� R� TD� ,� R� TC� ,� or� V� REF� and� GND� to� RCSET� sets� a�

�threshold� that� is� compared� to� the� voltage� on� the� timing� capacitor,�

�C� T� .� The� resistor� divider� voltage� divided� by� 2� corresponds� to� the�

�duty� cycle� below� which� a� short� circuit� can� exist.�

�D� SC� =� -------------------� ?� D� max�

�FIGURE� 9.� OC� RECOVERY� PRIOR� TO� SHUTDOWN�

�V� SCSET�

�2�

�(EQ.� 12)�

�If� the� overcurrent� condition� is� removed� prior� to� a� shutdown,� a�

�recovery� can� occur� as� indicated� in� Figure� 9.� When� the� load�

�decreases� below� the� overcurrent� threshold� and� an� additional�

�50� μ� s� elapses� without� the� SS� dropping� below� 4.25V,� the�

�overcurrent� circuitry� resets� and� the� soft-start� voltage� recovers.�

�The� duration� of� the� OC� shutdown� period� can� be� increased� by�

�adding� a� resistor� between� VREF� and� SS.� The� value� of� the�

�resistor� must� be� large� enough� so� that� the� minimum� specified�

�SS� discharge� current� is� not� exceeded.� Using� a� 422k� Ω� resistor,�

�for� example,� will� result� in� a� small� current� being� injected� into�

�SS,� effectively� reducing� the� discharge� current.� This� will� nearly�

�double� the� OFF� time.� The� external� pull-up� resistor� will� also�

�decrease� the� SS� duration,� so� its� effect� should� be� considered�

�when� selecting� the� value� of� the� SS� capacitor.�

�Latching� OC� shutdown� is� also� possible� by� using� a� lower� valued�

�resistor� between� VREF� and� SS.� If� the� SS� node� is� not� allowed� to�

�discharge� below� the� SS� reset� threshold,� the� IC� will� not� recover�

�from� an� overcurrent� fault.� The� value� of� the� resistor� must� be� low�

�enough� so� that� the� maximum� specified� discharge� current� is�

�not� sufficient� to� pull� SS� below� 0.33V.� A� 200k� Ω� resistor,� for�

�example,� prevents� SS� from� discharging� below� ~0.4V.� Again,�

�the� external� pull-up� resistor� will� decrease� the� SS� duration,� so�

�its� effect� should� be� considered� when� selecting� the� value� of� the�

�SS� capacitor.�

�12�

�where� D� SC� is� the� maximum� short� circuit� duty� cycle,� V� SCSET� is�

�the� voltage� applied� to� SCSET,� and� D� max� is� the� maximum� duty�

�cycle.� If� the� timing� capacitor� voltage� fails� to� exceed� the�

�threshold� before� an� overcurrent� pulse� is� detected,� a� short�

�circuit� condition� exists.� A� shutdown� will� occur� if� 8� short� circuit�

�events� occur� within� 32� oscillator� cycles.� Once� shutdown�

�occurs,� SS� will� discharge� through� a� 15μA� current� source.� A�

�new� soft-start� cycle� will� begin� when� SS� reaches� 0.27V.�

�Latching� shutdown� may� be� implemented� in� the� same� manner�

�as� described� in� the� overcurrent� section.� Short� circuit� shutdown�

�is� enabled� once� the� soft-start� cycle� is� complete.� Connecting�

�SCSET� to� GND� inhibits� short� circuit� shutdown.�

�If� either� R� TC� ar� R� TD� are� used� as� the� voltage� source� for� the�

�divider,� the� effect� of� the� SCSET� divider� must� be� included� in� the�

�timing� calculations� since� the� current� sourced� from� R� TC� and�

�R� TD� determine� the� charge� and� discharge� currents� for� the�

�timing� capacitor.� Typically� the� resistor� between� either� R� TC� or�

�R� TD� and� GND� is� formed� by� two� series� resistors� with� the� center�

�node� connected� to� SCSET.�

�Alternatively,� SCSET� may� be� set� using� a� voltage� between� 0V�

�and� 2V.� This� voltage� divided� by� 2� determines� the� percentage� of�

�the� maximum� duty� cycle� that� corresponds� to� a� short� circuit�

�when� current� limit� is� active.� For� example,� if� the� maximum� duty�

�cycle� is� 95%� and� 1V� is� applied� to� SCSET,� then� the� short� circuit�

�duty� cycle� is� 50%� of� 95%� or� 47.5%.�

�FN9195.3�

�February� 9,� 2012�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL6741IV-T | IC REG CTRLR PWM CM 16-TSSOP |

| ISL6742AAZA-T | IC REG CTRLR PWM CM/VM 16-QSOP |

| ISL6744AABZ | IC REG CTRLR PWM VM 8-SOIC |

| ISL6744AU-T | IC REG CTRLR BUCK PWM VM 8-MSOP |

| ISL6745AAUZ | IC REG CTRLR PWM VM 10-MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6740AIVZA-T | 功能描述:IC REG CTRLR PWM VM 16-TSSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL6740EVAL1 | 功能描述:EVALUATION BOARD 1 ISL6740 RoHS:否 类别:编程器,开发系统 >> 评估板 - DC/DC 与 AC/DC(离线)SMPS 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:True Shutdown™ 主要目的:DC/DC,步升 输出及类型:1,非隔离 功率 - 输出:- 输出电压:- 电流 - 输出:1A 输入电压:2.5 V ~ 5.5 V 稳压器拓扑结构:升压 频率 - 开关:3MHz 板类型:完全填充 已供物品:板 已用 IC / 零件:MAX8969 |

| ISL6740EVAL2 | 功能描述:EVALUATION BOARD 2 ISL6740 RoHS:否 类别:编程器,开发系统 >> 过时/停产零件编号 系列:- 标准包装:1 系列:- 传感器类型:CMOS 成像,彩色(RGB) 传感范围:WVGA 接口:I²C 灵敏度:60 fps 电源电压:5.7 V ~ 6.3 V 嵌入式:否 已供物品:成像器板 已用 IC / 零件:KAC-00401 相关产品:4H2099-ND - SENSOR IMAGE WVGA COLOR 48-PQFP4H2094-ND - SENSOR IMAGE WVGA MONO 48-PQFP |

| ISL6740EVAL2Z | 功能描述:EVALUATION BOARD 2 ISL6740 RoHS:是 类别:编程器,开发系统 >> 评估板 - DC/DC 与 AC/DC(离线)SMPS 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:True Shutdown™ 主要目的:DC/DC,步升 输出及类型:1,非隔离 功率 - 输出:- 输出电压:- 电流 - 输出:1A 输入电压:2.5 V ~ 5.5 V 稳压器拓扑结构:升压 频率 - 开关:3MHz 板类型:完全填充 已供物品:板 已用 IC / 零件:MAX8969 |

| ISL6740EVAL3Z | 制造商:Intersil Corporation 功能描述:ISL6740 EVALUATION BOARD 3 - ROHS COMPLIANT - SOIC - DSL - Bulk 制造商:Intersil Corporation 功能描述:Power Management IC Development Tools ISL6740 EVAL RD 3 ROHS CMPL DSL |

发布紧急采购,3分钟左右您将得到回复。