参数资料

| 型号: | KS8001S |

| 厂商: | Micrel Inc |

| 文件页数: | 10/44页 |

| 文件大小: | 0K |

| 描述: | TXRX 10/100 LINKMD 3.3V 48-SSOP |

| 标准包装: | 30 |

| 类型: | 收发器 |

| 驱动器/接收器数: | 1/1 |

| 规程: | IEEE 802 |

| 电源电压: | 1.8 V ~ 3.3 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-BSSOP(0.295",7.50mm 宽) |

| 供应商设备封装: | 48-SSOP |

| 包装: | 管件 |

| 配用: | KS8001L-EVAL-ND - EVAL KIT EXPERIMENTAL KS8001L |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

KS8001

Micrel

May 2005 – SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

KS8001

MICREL CONFIDENTIAL. DO NOT DISTRIBUTE.

18

CRS

RX_DV

RXD0

RXD1

RXD2

RXD3

RXD4

RXD5

RXD6

RXD7

X

0

RX_ER

from

previous

frame

Speed

0=10Mbit

1=100Mbit

Duplex

0=Half

1=Full

Link

0=Down

1=Up

Jabber

0=OK

1=Error

Upper

Nibble

0=invalid

1=valid

False

Carrier

Detected

1

X

1

One Data Byte (Two MII Data Nibble)

TXD7 – 0 Encoding

Inter-frame status bit RXD5 conveys the validity of the upper nibble of the byte of the previous frame. Inter-frame status bit RXD0

indicates whether or not the PHY detected an error somewhere on the previous frame. Both of these bits should be valid in the

segment immediately following a frame, and should stay valid until the first data segment of the next frame begins.

When asserted, inter-frame status bit RXD6 indicates that the PHY has detected a false carrier event.

In order to send receive data to the MAC synchronous to the reference clock, the PHY must pass the data through an elasticity FIFO

to handle any difference between the reference clock rate and the clock at the packet source. The Ethernet specification calls for

packet data to be referenced to a clock with a frequency tolerance of 100ppm (0.01%); however, it is not uncommon to encounter

Ethernet stations with clocks that have frequency errors up to 0.1%. Therefore, the elasticity FIFO should be at least 27 bits * long,

filling to the half-way point before beginning valid data transfer via RX. RX_ER should be asserted if, during the reception of a frame,

this fifo overflows or underflows.

Only RXD and RX_DV should be passed through the elasticity FIFO. CRS should not be passed through the elasticity FIFO. Instead,

CRS should be asserted for the time the ‘wire’ is busy receiving a frame.

Transmit Path

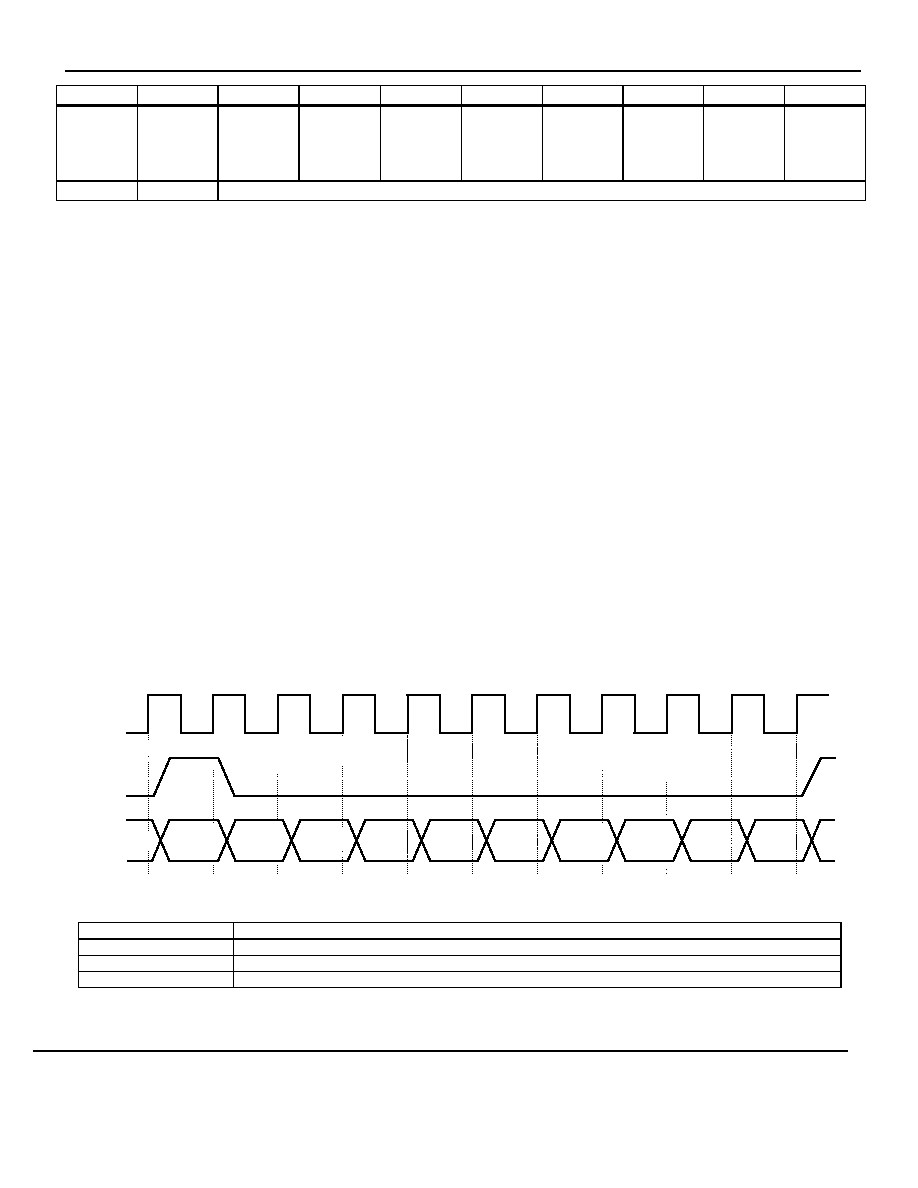

Transmit data and control information are signaled in ten bit segments, just like the receive path. In 100Mbit mode, each segment

represents anew byte of data. In 10Mbit mode each segment is repeated ten times; therefore, every ten segments represents a new

byte of data. The PHY can sample any one of every 10 segments in 10Mbit mode.

Segment boundaries are delimited by SYNC. The MAC continuously generates a pulse on SYNC every 10 clocks.

Transmit Sequence Diagram

TX_ER

TX_EN

TXD0

TXD1

TXD2

TXD3

TXD4

TXD5

TXD6

TXD7

TX_CLK

TX_SYNC

TX

Bits

Purpose

TX_EN

Transmit Enable – identical to MII

TX_ER

Transmit Error – identical to MII

TXD7-0

Encoded Data – see TXD7-0 Encoding Table

TX- Bit Description

相关PDF资料 |

PDF描述 |

|---|---|

| NB7L216MN | IC RECEIVER/DRIVER DIFF 16-QFN |

| M83723/75W10028 | CONN PLUG 2POS STRAIGHT W/SCKT |

| VI-B41-IV-B1 | CONVERTER MOD DC/DC 12V 150W |

| VI-J7Z-EY-F3 | CONVERTER MOD DC/DC 2V 20W |

| D38999/24WJ43PA | CONN RCPT 43POS JAM NUT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KS8001S TR | 功能描述:TXRX 10/100 LINKMD 3.3V 48-SSOP RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,140 系列:AU 类型:收发器 驱动器/接收器数:1/1 规程:CAN 电源电压:5.3 V ~ 27 V 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SO 包装:管件 其它名称:935267940512AU5790D14AU5790D14-ND |

| KS8001SI | 功能描述:TXRX 10/100 LINKMD 3.3V 48-SSOP RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:1,140 系列:AU 类型:收发器 驱动器/接收器数:1/1 规程:CAN 电源电压:5.3 V ~ 27 V 安装类型:表面贴装 封装/外壳:14-SOIC(0.154",3.90mm 宽) 供应商设备封装:14-SO 包装:管件 其它名称:935267940512AU5790D14AU5790D14-ND |

| KS800A500-1800V Y40KSEA | 制造商:LIUJING 制造商全称:LIUJING 功能描述:可控硅、晶闸管 |

| KS800A500-1800V Y40KSE | 制造商:LIUJING 制造商全称:LIUJING 功能描述:可控硅、晶闸管 |

| KS8081 | 功能描述:IC SWITCH 10/100 3PORT 128PQFP RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。