参数资料

| 型号: | KS8999I |

| 厂商: | Micrel Inc |

| 文件页数: | 9/52页 |

| 文件大小: | 0K |

| 描述: | IC SWITCH 9-PORT 10/100 208-PQFP |

| 标准包装: | 100 |

| 系列: | * |

| 类型: | * |

| 应用: | * |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-MQFP,208-PQFP |

| 供应商设备封装: | 208-PQFP(28x28) |

| 包装: | 散装 |

| 配用: | 576-1023-ND - BOARD EVAL EXPERIMENT FOR KS8999 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

January 2005

17

KS8999

Micrel

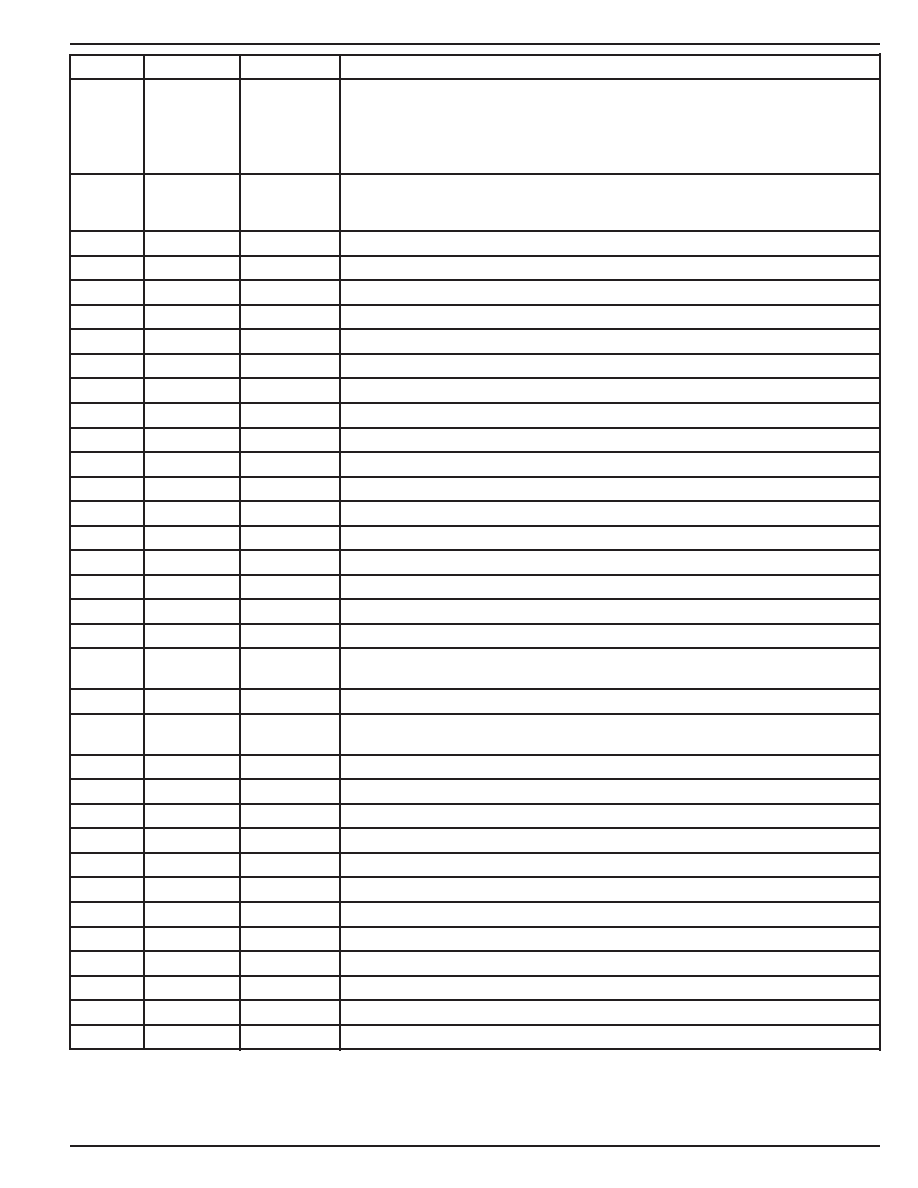

Group

I/O Names

Active Status

Description(Note 1)

PRSV

H

Priority buffer reserve – reserves 6KB of buffer space for the priority traffic if enabled.

0 = No priority reserve

1 = Reserve 6KB for priority traffic

Note: This is also controlled by the EEPROM registers (register 2 bit 1). The value in

the EEPROM supercedes this pin.

CFGMODE

H

Selects between EEPROM or processor for programming interface.

0 = Processor interface

1 = EEPROM interface or not programmed on this interface (SCL / SDA not used)

X1

Clock

External crystal or clock input

X2

Clock

Used when other polarity of crystal is needed. This is unused for a normal clock input.

SCL

Clock

Clock for EEPROM

SDA

I/O

Serial data for EEPROM

RST#

L

System reset

TEST

TESTEN

H

Factory test input – tie low for normal operation

SCANEN

H

Factory test input – tie low for normal operation

MUX[1:2]

H

Factory test input – leave open for normal operation

AOUT

H

Factory test output – leave open for normal operation

DOUT

H

Factory test output – leave open for normal operation

AOUT2

H

Factory test output – leave open for normal operation

DOUT2

H

Factory test output – leave open for normal operation

BTOUT

H

Factory test output – leave open for normal operation

CTOUT

H

Factory test output – leave open for normal operation

BTOUT2

H

Factory test output – leave open for normal operation

CTOUT2

H

Factory test output – leave open for normal operation

TEST[1:2]

H

Factory test inputs – leave open for normal operation

AUTOMDIX

H

F/U = Enable Auto MDI/MDIX (normal operation)

D = Disable Auto MDI/MDIX

T[1:3] & T[5]

H

Factory test inputs – leave open (float) for normal operation

T[4]

H

F/D = normal operation (default)

U = Disable FEF

QH[2:5]

H

Factory test outputs – leave open for normal operation

QL[2:5]

H

Factory test outputs – leave open for normal operation

IO_SWM

H

Factory test input – tie high for normal operation

RLPBK

H

Factory test input – tie low for normal operation

BIST

H

Factory test input – tie low for normal operation

PWR

VDD_RX

2.0V for equalizer

GND_RX

Ground for equalizer

VDD_TX

2.0V for transmit circuitry

GND_TX

Ground for transmit circuitry

VDD_RCV

2.0V for clock recovery circuitry

GND_RCV

Ground for clock recovery

VDD_PLLTX

2.0V for phase locked loop circuitry

Note 1.

All unmanaged programming takes place at reset time only. For unmanaged programming: F = Float, D = Pull-down, U = Pull-up.

See

“Reference Circuits” section.

相关PDF资料 |

PDF描述 |

|---|---|

| KSZ8001LI TR | IC TXRX PHY 10/100 3.3V 48LQFP |

| KSZ8031RNLI | TXRX PHY 10/100 3.3V 24-QFN |

| KSZ8041MLL TR | TXRX 10/100 3.3V PHY MII 48LQFP |

| KSZ8041NLA3TR | TRANSCEIVER 10/100 32-MLF |

| KSZ8041NLJ TR | TXRX PHY 10/100 3.3V 32MLF |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KS9/KSE9/59/103/115 | 制造商:PEPPERL+FUCHS 功能描述:Through beam cable sensor,PNP o/p 250mm |

| KS9~11 | 制造商:Tohodenzai 功能描述: |

| KS9~12B | 制造商:Tohodenzai 功能描述: |

| KS900A | 制造商:ALC 功能描述:ALCO CLEAR KNOB S9B6B |

| KS900A1/4 | 功能描述:旋钮和转盘 KNOB AL W/SKIRT 1/4 RoHS:否 制造商:Davies Molding 材料:Phenolic 设计:Set Screw 轴尺寸:0.25 in 直径:3/4 in 颜色:Black 指示器型式:Line |

发布紧急采购,3分钟左右您将得到回复。