- 您现在的位置:买卖IC网 > PDF目录11595 > KSZ8851-16MLL (Micrel Inc)IC CTLR MAC/PHY NON-PCI 48-LQFP PDF资料下载

参数资料

| 型号: | KSZ8851-16MLL |

| 厂商: | Micrel Inc |

| 文件页数: | 22/84页 |

| 文件大小: | 0K |

| 描述: | IC CTLR MAC/PHY NON-PCI 48-LQFP |

| 产品培训模块: | KSZ8851 10/100 Embedded Controllers |

| 标准包装: | 250 |

| 控制器类型: | 以太网控制器,MAC/PHY |

| 接口: | 总线 |

| 电源电压: | 1.8V,2.5V,3.3V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 托盘 |

| 产品目录页面: | 1081 (CN2011-ZH PDF) |

| 配用: | 576-3292-ND - BOARD EVALUATION KSZ8851-16MLL |

| 其它名称: | 576-3252 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

Micrel, Inc.

KSZ8851-16MLL/MLLI

March 11, 2014

29

Revision 2.2

Frame Queue (RXQ) Frame Format

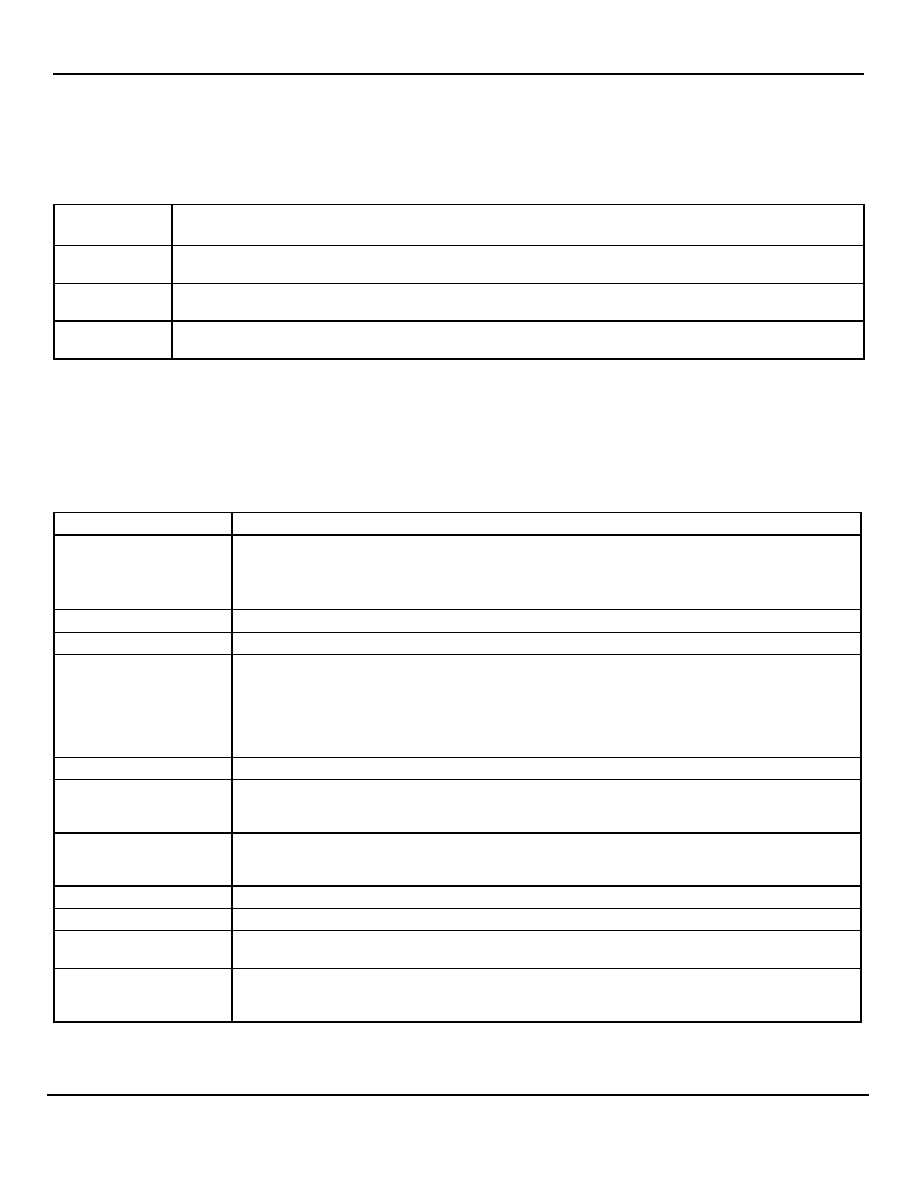

The frame format for the receive queue is shown in Table 9. The first word contains the status information for the frame

received. The second word is the total number of bytes of the RX frame. Following that is the packet data area. The

packet data area holds the frame itself. It includes the CRC checksum.

Packet Memory

Address Offset

Bit 15

Bit 0

2

nd Byte

1

st Byte

0

Status Word

(High byte and low byte need to swap in Big-Endian mode. Also see description in RXFHSR register)

2

Byte Count

(High byte and low byte need to swap in Big-Endian mode. Also see description in RXFHBCR register)

4 - up

Receive Packet Data

(maximum size is 2000)

Table 9. Frame Format for Receive Queue

Frame Receiving Path Operation in RXQ

This section describes the typical register settings for receiving packets from KSZ8851-16MLL to host processor with

generic bus interface. User can use the default value for most of the receive registers. Table 10 describes all registers

which need to be set and used for receiving single or multiple frames.

Register Name[bit](offset)

Description

RXCR1(0x74)

RXCR2(0x76)

Set receive control function as below:

Set RXCR1[10] to enable receiving flow control. Set RXCR1[0] to enable receiving block operation.

Set receive checksum check for ICMP, UDP, TCP and IP packet.

Set receive address filtering scheme as shown in the Table 3.

RXFHSR[15:0](0x7C)

This register (read only) indicates the current received frame header status information.

RXFHBCR[11:0](0x7E)

This register (read only) indicates the current received frame header byte count information.

RXQCR[12:3](0x82)

Set RXQ control function as below:

Set bit 3 to start DMA access from host CPU either read (receive frame data) or write (transmit data

frame). Set bit 4 to automatically enable RXQ frame buffer dequeue. Set bit 5 to enable RX frame count

threshold and read bit 10 for status. Set bit 6 to enable RX data byte count threshold and read bit 11 for

status. Set bit 7 to enable RX frame duration timer threshold and read bit 12 for status. Set bit 9 enable

RX IP header two-byte offset.

RXFDPR[14](0x86)

Set bit 14 to enable RXQ address register increments automatically on accesses to the data register.

RXDTTR[15:0](0x8C)

To program received frame duration timer value. When Rx frame duration in RXQ exceeds this

threshold in 1uS interval count and bit 7 of RXQCR register is set to 1, the KSZ8851-16MLL will

generate RX interrupt in ISR[13] and indicate the status in RXQCR[12].

RXDBCTR[15:0](0x8E)

To program received data byte count value. When the number of received bytes in RXQ exceeds this

threshold in byte count and bit 6 of RXQCR register is set to 1, the KSZ8851-16MLL will generate RX

interrupt in ISR[13] and indicate the status in RXQCR[11].

IER[13](0x90)

Set bit 13 to enable receive interrupt in Interrupt Enable Register.

ISR[15:0](0x92)

Write 1 (0xFFFF) to clear all interrupt status bits after interrupt occurred in Interrupt Status Register.

RXFCTR[15:8](0x9C)

Rx frame count read only. To indicate the total received frame in RXQ frame buffer when receive

interrupt (bit 13 in ISR) occurred.

RXFCTR[7:0](0x9C)

To program received frame count value. When the number of received frames in RXQ exceeds or

equals to this threshold value and bit 5 of RXQCR register is set to 1, the KSZ8851-16MLL will

generate RX interrupt in ISR[13] and indicate the status in RXQCR[10].

Table 10. Registers Setting for Receive Function Block

相关PDF资料 |

PDF描述 |

|---|---|

| KSZ8873RLL | IC ETHERNET SWITCH 3PORT 64-LQFP |

| KSZ8851-16MQLI | IC CTLR MAC/PHY NON-PCI 128-PQFP |

| KSZ8851-16MQL | IC CTLR MAC/PHY NON-PCI 128-PQFP |

| LTC4278CDKD#PBF | IC PD IEEE 802.3AT 25.5W 32-DFN |

| KSZ8873MLL | IC ETHERNET SWITCH 3PORT 64-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8851-16MLL TR | 功能描述:以太网 IC Single Ethernet Port + Generic (16-bit) Bus Interface(Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLL-EVAL | 功能描述:以太网开发工具 Single Ethernet Port + Generic (16-bit) Bus Interface(Lead Free) Eval Board RoHS:否 制造商:Micrel 产品:Evaluation Boards 类型:Ethernet Transceivers 工具用于评估:KSZ8873RLL 接口类型:RMII 工作电源电压: |

| KSZ8851-16MLL-EVAL | 制造商:Micrel Inc 功能描述:BOARD EVALUATION FOR KSZ8851-16MLL |

| KSZ8851-16MLLI | 功能描述:以太网 IC 10/100BT Ethernet MAC + PHY with Generic (8, 16-bit) Bus Interface (I-Temp, Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8851-16MLLI TR | 功能描述:以太网 IC 10/100BT Ethernet MAC + PHY with Generic (8, 16-bit) Bus Interface (I-Temp, Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。