参数资料

| 型号: | KSZ8995M |

| 厂商: | Micrel Inc |

| 文件页数: | 8/73页 |

| 文件大小: | 0K |

| 描述: | IC SWITCH 10/100 5PORT 128PQFP |

| 标准包装: | 66 |

| 系列: | * |

| 类型: | * |

| 应用: | * |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 128-BFQFP |

| 供应商设备封装: | 128-PQFP(14x20) |

| 包装: | 托盘 |

| 产品目录页面: | 1081 (CN2011-ZH PDF) |

| 配用: | 576-1607-ND - BOARD EVAL EXPERIMENT KSZ8995MA |

| 其它名称: | 576-1038 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

KS8995M

Micrel

M9999-120403

16

December 2003

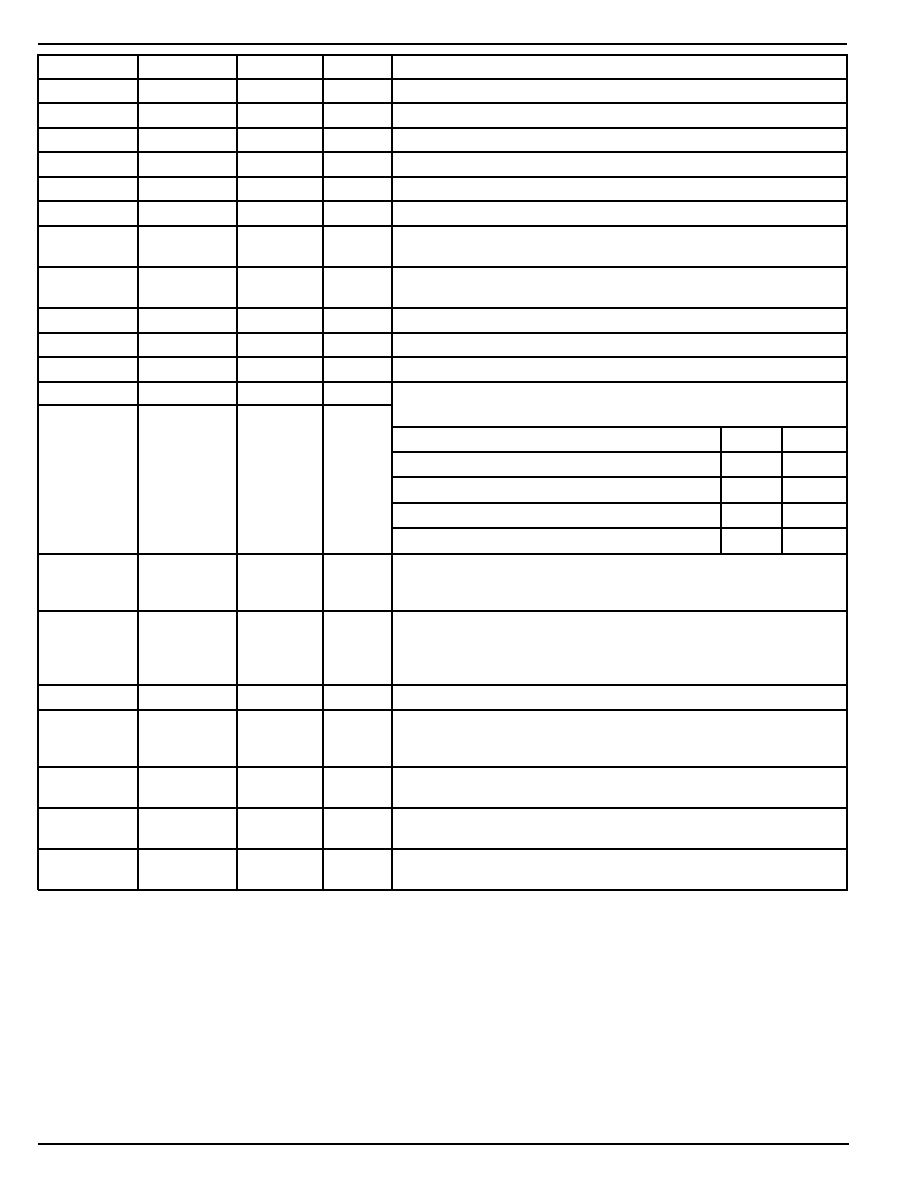

Pin Number

Pin Name

Type(1)

Port

Pin Function

97

LED3-1

Ipu/O

3

LED indicator 1

96

LED3-2

Ipu/O

3

LED indicator 2

95

LED4-0

Ipu/O

4

LED indicator 0

94

LED4-1

Ipu/O

4

LED indicator 1

93

LED4-2

Ipu/O

4

LED indicator 2

92

LED5-0

Ipu/O

5

LED indicator 0

91

LED5-1

Ipu/O

5

LED indicator 1. Strap option: PU (default): enable PHY MII I/F.

PD: tristate all PHY MII output. See

“pin# 86 SCONF1.”

90

LED5-2

Ipu/O

5

LED indicator 2. Strap option: Aging setup. See

“Aging” section.

(default) = Aging Enable; PD = Aging disable

107

MDC

Ipu

All

Switch or PHY[5] MII management data clock.

108

MDIO

I/O

All

Switch or PHY[5] MII management data I/O.

1

TEST1

NC

NC for normal operation. Factory test pin.

45

MUX1

NC

MUX1 and MUX2 should be left unconnected for normal operation.

46

MUX2

NC

They are factory test pins.

Mode

Mux1

Mux2

Normal Operation

NC

Remote Analog Loopback Mode for Testing only

0

1

Reserved

1

0

Power Save Mode for Testing only

1

68

PCOL

Ipd/O

5

PHY[5] MII collision detect/Force flow control. See

“Register 18.”

For port 4 only. PD (default) = No force flow control. PU = Force flow

control.

67

PCRS

Ipd/O

5

PHY[5] MII carrier sense/Force duplex mode See

“Register 28.”

For port 4 only. PD (default) = Force half-duplex if auto-negotiation is

disabled or fails. PU = Force full-duplex if auto-negotiation is disabled

or fails.

60

PMRXC

O

5

PHY[5] MII receive clock. PHY mode MII.

65

PMRXD0

Ipd/O

5

PHY[5] MII receive bit 0. Strap option: PD (default) = disable

aggressive back-off algorithm in half-duplex mode; PU = enable for

performance enhancement.

64

PMRXD1

Ipd/O

5

PHY[5] MII receive bit 1. Strap option: PD (default) = drop excessive

collision packets; PU = does not drop excessive collision packets.

63

PMRXD2

Ipd/O

5

PHY[5] MII receive bit 2. Strap option: PD (default) = disable back

pressure; PU = enable back pressure.

62

PMRXD3

Ipd/O

5

PHY[5] MII receive bit 3. Strap option: PD (default) = enable flow

control; PU = disable flow control.

Note:

1. P = Power supply

I = Input

O = Output

I/O = Bi-directional

Gnd = Ground

Ipu = Input w/ internal pull-up

Ipd = Input w/ internal pull-down

Ipd/O = Input w/ internal pull-down during reset, output pin otherwise

Ipu/O = Input w/ internal pull-up during reset, output pin otherwise

PU = Strap pin pull-up

PD = Strap pin pull-down

Otri = Output tristated

NC = No Connect

相关PDF资料 |

PDF描述 |

|---|---|

| RSM40DTAT | CONN EDGECARD 80POS R/A .156 SLD |

| LFEC6E-3QN208C | IC FPGA 6.1KLUTS 147I/O 208-PQFP |

| LFEC6E-3Q208C | IC FPGA 6.1KLUTS 147I/O 208-PQFP |

| RMM40DTAT | CONN EDGECARD 80POS R/A .156 SLD |

| LFXP3E-5Q208C | IC FPGA 3.1KLUTS 136I/O 208-PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8995MA | 功能描述:以太网 IC 5 Port 10/100 Switch with PHY and Frame Buffers (Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8995MA4 | 功能描述:IC SWITCH 5-PORT 10/100 128PQFP RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| KSZ8995MAB3 | 功能描述:IC SWITCH 5-PORT 10/100 128PQFP RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| KSZ8995MA-EVAL | 功能描述:以太网开发工具 KSZ8995MA Evaluation Board RoHS:否 制造商:Micrel 产品:Evaluation Boards 类型:Ethernet Transceivers 工具用于评估:KSZ8873RLL 接口类型:RMII 工作电源电压: |

| KSZ8995MAI | 功能描述:以太网 IC 5 Port 10/100 Switch with PHY and Frame Buffers (Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。