- 您现在的位置:买卖IC网 > PDF目录177656 > LC4256B-10F256AI (LATTICE SEMICONDUCTOR CORP) PDF资料下载

参数资料

| 型号: | LC4256B-10F256AI |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 中文描述: | EE PLD, 10 ns, PBGA256 |

| 封装: | FPBGA-256 |

| 文件页数: | 1/99页 |

| 文件大小: | 760K |

| 代理商: | LC4256B-10F256AI |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页

www.latticesemi.com

1

DS1020_23.1

ispMACH 4000V/B/C/Z Family

3.3V/2.5V/1.8V In-System Programmable

SuperFAST High Density PLDs

May 2009

Data Sheet DS1020

TM

2009 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Features

High Performance

fMAX = 400MHz maximum operating frequency

tPD = 2.5ns propagation delay

Up to four global clock pins with programmable

clock polarity control

Up to 80 PTs per output

Ease of Design

Enhanced macrocells with individual clock,

reset, preset and clock enable controls

Up to four global OE controls

Individual local OE control per I/O pin

Excellent First-Time-Fit

TM and refit

Fast path, SpeedLocking

TM Path, and wide-PT

path

Wide input gating (36 input logic blocks) for fast

counters, state machines and address decoders

Zero Power (ispMACH 4000Z) and Low

Power (ispMACH 4000V/B/C)

Typical static current 10A (4032Z)

Typical static current 1.3mA (4000C)

1.8V core low dynamic power

ispMACH 4000Z operational down to 1.6V VCC

Broad Device Offering

Multiple temperature range support

– Commercial: 0 to 90°C junction (Tj)

– Industrial: -40 to 105°C junction (Tj)

– Extended: -40 to 130°C junction (Tj)

For AEC-Q100 compliant devices, refer to

Easy System Integration

Superior solution for power sensitive consumer

applications

Operation with 3.3V, 2.5V or 1.8V LVCMOS I/O

Operation with 3.3V (4000V), 2.5V (4000B) or

1.8V (4000C/Z) supplies

5V tolerant I/O for LVCMOS 3.3, LVTTL, and PCI

interfaces

Hot-socketing

Open-drain capability

Input pull-up, pull-down or bus-keeper

Programmable output slew rate

3.3V PCI compatible

IEEE 1149.1 boundary scan testable

3.3V/2.5V/1.8V In-System Programmable

(ISP) using IEEE 1532 compliant interface

I/O pins with fast setup path

Lead-free package options

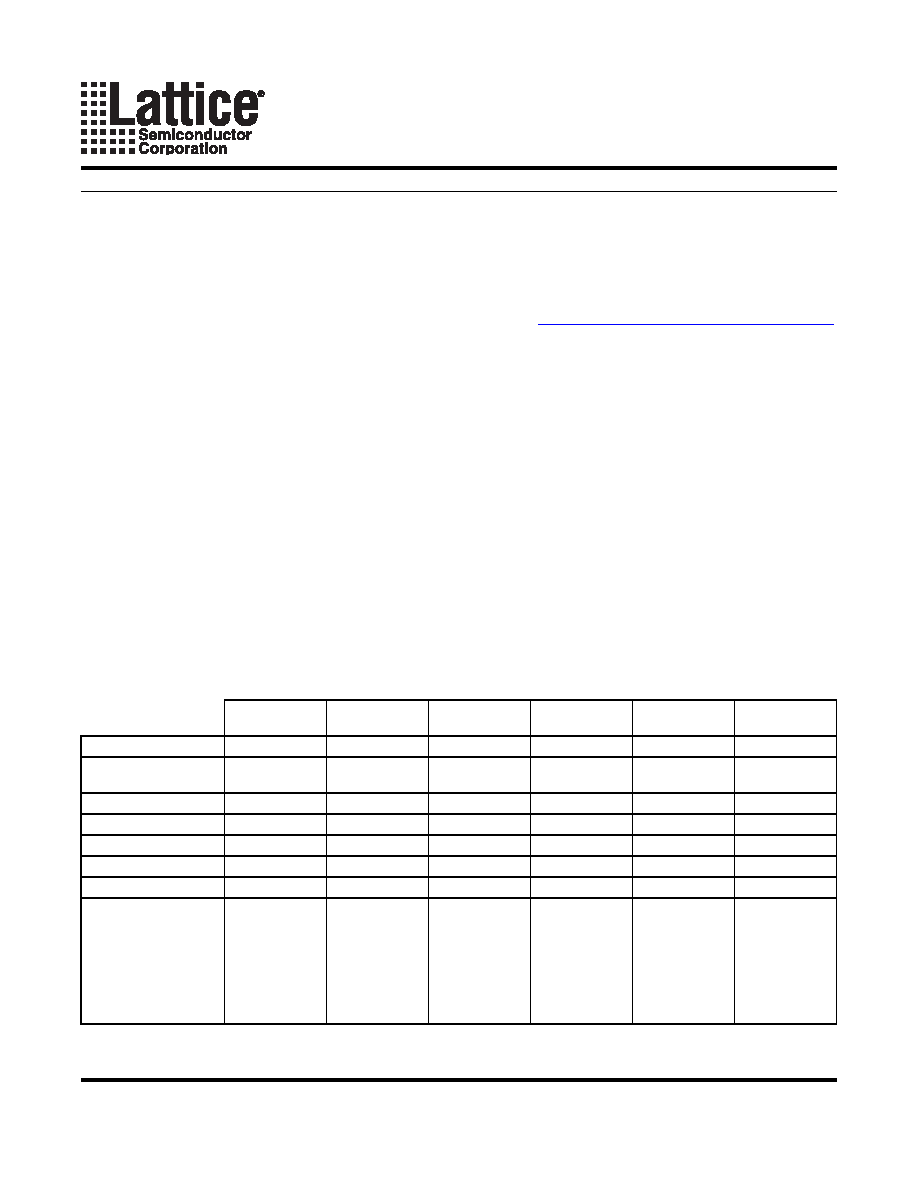

Table 1. ispMACH 4000V/B/C Family Selection Guide

ispMACH

4032V/B/C

ispMACH

4064V/B/C

ispMACH

4128V/B/C

ispMACH

4256V/B/C

ispMACH

4384V/B/C

ispMACH

4512V/B/C

Macrocells

32

64

128

256

384

512

I/O + Dedicated Inputs

30+2/32+4

30+2/32+4/

64+10

64+10/92+4/

96+4

64+10/96+14/

128+4/160+4

128+4/192+4

128+4/208+4

tPD (ns)

2.52.5

2.73.0

3.53.5

tS (ns)

1.81.8

1.82.0

2.02.0

tCO (ns)

2.22.2

2.72.7

fMAX (MHz)

400

333

322

Supply Voltages (V)

3.3/2.5/1.8V

Pins/Package

44 TQFP

48 TQFP

44 TQFP

48 TQFP

100 TQFP

128 TQFP

144 TQFP

1

100 TQFP

144 TQFP

1

176 TQFP

256 ftBGA

2/

fpBGA

2, 3

176 TQFP

256 ftBGA/

fpBGA

3

176 TQFP

256 ftBGA/

fpBGA

3

1. 3.3V (4000V) only.

2. 128-I/O and 160-I/O configurations.

3. Use 256 ftBGA package for all new designs. Refer to PCN#14A-07 for 256 fpBGA package discontinuance.

相关PDF资料 |

PDF描述 |

|---|---|

| LC4064C-5T100C | |

| LC4128ZC-42M132C | |

| LC4256C-10T100I | |

| LC4256V-5T176I | |

| LC4384C-35FT256C | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC4256B-10F256AI1 | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4256B-10F256BI | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC4256B-10F256BI1 | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

| LC4256B-10FN256AI | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAMMABLE SUPER FAST HI DENSITY PLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC4256B-10FN256AI1 | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V/2.5V/1.8V In-System Programmable SuperFAST High Density PLDs |

发布紧急采购,3分钟左右您将得到回复。