- 您现在的位置:买卖IC网 > PDF目录378649 > LF3310QC15 (LOGIC DEVICES INC) Horizontal / Vertical Digital Image Filter PDF资料下载

参数资料

| 型号: | LF3310QC15 |

| 厂商: | LOGIC DEVICES INC |

| 元件分类: | 数字信号处理外设 |

| 英文描述: | Horizontal / Vertical Digital Image Filter |

| 中文描述: | 12-BIT, DSP-DIGITAL FILTER, PQFP144 |

| 封装: | PLASTIC, QFP-144 |

| 文件页数: | 6/21页 |

| 文件大小: | 287K |

| 代理商: | LF3310QC15 |

DEVICES INCORPORATED

LF3310

Horizontal / Vertical Digital Image Filter

6

Video Imaging Products

11/08/2001-LDS.3310-H

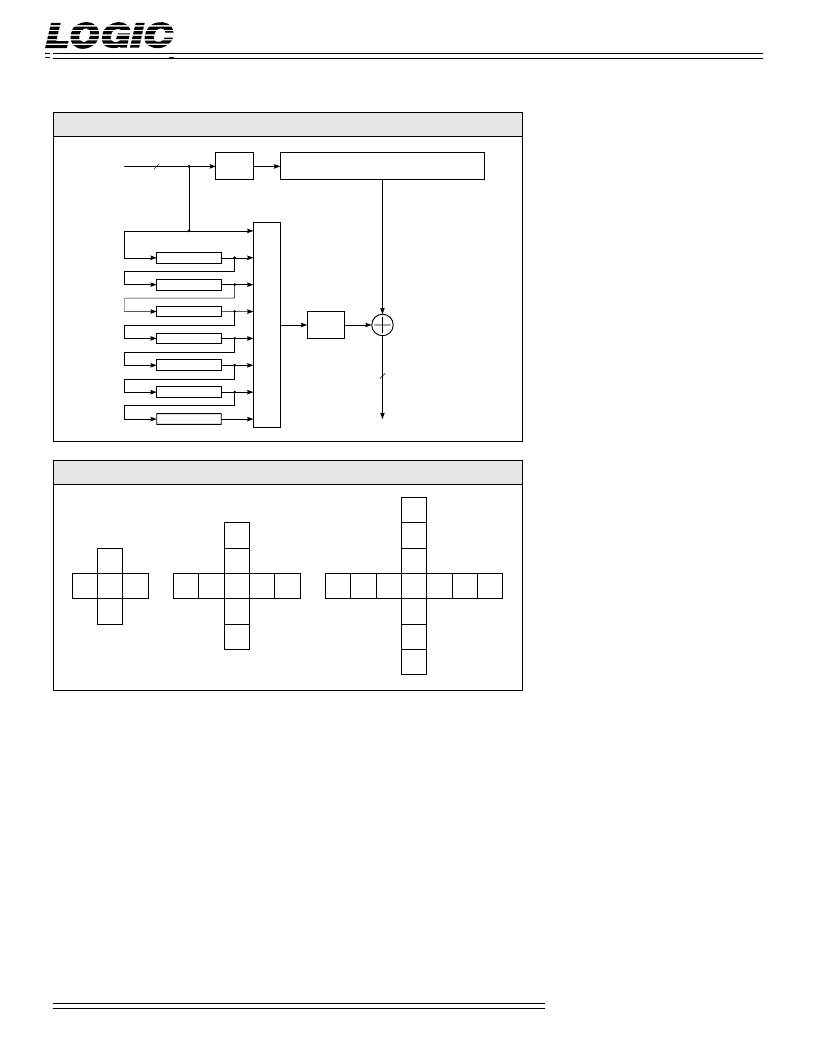

The HV Filter can handle kernel sizes

of 3-3, 5-5, and 7-7 (see Figure 7).

Data delay elements at the input of

the horizontal filter and the output of

the vertical filter are used to properly

align data so that the orthogonal

kernel is implemented correctly. The

data delays are automatically set to

the correct lengths based on the

programmed length of the line buffers

and the kernel size.

Kernel sizes of 3-3, 5-5, and 7-7

require that the horizontal filter’s

output be delayed by LB – 2, 2(LB) – 3,

and 3(LB) – 4 clock cycles respectively

before being added to the vertical

filter’s output (LB is the programmed

line buffer length). The data delay at

the input of the horizontal filter

handles the LB, 2(LB), and 3(LB)

delays. The data delay at the output

of the vertical filter handles the – 2, – 3,

and – 4 delays. For example, if the line

buffers are programmed for a length of

720 and a 5–5 kernel is selected, the

horizontal filter input data delay will

be 1440 clock cycles and the vertical

filter output data delay will be 3 clock

cycles.

It is important to note that the first 3,

5, or 7 multipliers of the horizontal

and vertical filters must be used in

Orthogonal Mode. If other multipli-

ers are used, data from the horizontal

and vertical filters will not line up

correctly because the data delays are

calculated assuming that the first 3, 5,

or 7 multipliers are used. Also, the

ALUs in the horizontal filter should

be configured to accept data from the

forward I/ D Register path into ALU

Input A and force ALU Input B to 0.

FUNCTIONAL DESCRIPTION

Horizontal Filter

The horizontal filter is designed to

filter a digital image in the horizontal

dimension. This FIR filter can be

configured to have as many as 16-taps

when symmetric coefficient sets are

used and 8-taps when asymmetric

coefficient sets are used.

ALUs

The ALUs double the number of filter

taps available, when symmetric

coefficient sets are used, by

pre-adding data values which are

then multiplied by a common coeffi-

cient (see Figure 8). The ALUs can

perform two operations: A+B and

B–A. Bit 0 of Configuration Regis-

ter 0 determines the ALU operation.

A+B is used with even-symmetric

coefficient sets. B–A is used with

odd-symmetric coefficient sets. Also,

either the A or B operand may be set

to 0. Bits 1 and 2 of Configuration

Register 0 control the ALU inputs.

A+0 or B+0 are used with asymmetric

coefficient sets.

Interleave/Decimation Registers

The Interleave/ Decimation Registers

(I/ D Registers) feed the ALU inputs.

They allow the device to filter up to

sixteen data sets interleaved into the

same data stream without having to

separate the data sets. The I/ D

Registers should be set to a length

equal to the number of data sets

interleaved together. For example, if

two data sets are interleaved together,

the I/ D Registers should be set to a

length of two. Bits 1 through 4 of

Configuration Register 1 determine

F

IGURE

6.

O

RTHOGONAL

M

ODE

DIN

11-0

HORIZONTAL FILTER

V

LINE BUFFER

12

LINE BUFFER

LINE BUFFER

LINE BUFFER

LINE BUFFER

LINE BUFFER

LINE BUFFER

DOUT

11-0

12

DATA

DELAY

DATA

DELAY

F

IGURE

7.

3-3, 5-5,

AND

7-7 O

RTHOGONAL

K

ERNELS

V

2

V

3

HV

4

H

3

H

5

V

5

V

6

H

2

H

6

H

1

H

7

V

1

V

7

V

1

V

2

HV

3

H

2

H

4

V

4

V

5

H

1

H

5

V

1

HV

2

H

1

H

3

V

3

相关PDF资料 |

PDF描述 |

|---|---|

| LF3330QC12 | Vertical Digital Image Filter |

| LF3330QC15 | Vertical Digital Image Filter |

| LF43168 | Dual 8-Tap FIR Filter |

| LF43168JC15 | Digital Filter |

| LF43168JC22 | Digital Filter |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LF3310QC18 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Digital Filter |

| LF3310QC25 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Digital Filter |

| LF3311 | 制造商:LOGIC 制造商全称:LOGIC 功能描述:Horizontal / Vertical Digital Image Filter |

| LF3312 | 制造商:LOGIC 制造商全称:LOGIC 功能描述:12-Mbit Frame Buffer / FIFO |

| LF3320 | 制造商:LOGIC 制造商全称:LOGIC 功能描述:Horizontal Digital Image Filter |

发布紧急采购,3分钟左右您将得到回复。