- 您现在的位置:买卖IC网 > PDF目录30743 > LM1247AAG/NA/NOPB (NATIONAL SEMICONDUCTOR CORP) 3 CHANNEL, VIDEO PREAMPLIFIER, PDIP24 PDF资料下载

参数资料

| 型号: | LM1247AAG/NA/NOPB |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | 音频/视频放大 |

| 英文描述: | 3 CHANNEL, VIDEO PREAMPLIFIER, PDIP24 |

| 封装: | PLASTIC, DIP-24 |

| 文件页数: | 18/48页 |

| 文件大小: | 3141K |

| 代理商: | LM1247AAG/NA/NOPB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

LM1247 Address Map (Continued)

END-OF-SCREEN CODE

To signify the end of the window, a special End-of-Screen (EOS) code is used in place of a End-of-Line (EOL) code. There must

be at least one EOS code in the Page RAM to avoid unpredictable behaviour. This can be accomplished by clearing the RAM by

writinga0tobit3ofthe FRMCTRL1 Register, 0x8400, immediately after power up.

TABLE 13. End-of-Screen Code

ATTRIBUTE CODE

END-OF-SCREEN CODE

ATT[3:0]

0000000

0

Bits 7-0 are all zeros. Bits 11-0 will have the previously entered AC but this is not used and so these bits are “don’t cares”.

OSD CONTROL REGISTERS

These registers, shown in Table 14, control the size, position, enhanced features and ROM bank selection of up to two

independent OSD windows. Any bits marked as “X” are reserved and should be written to with zeros and should be ignored when

the register is read. Additional register detail is provided in the Control Register Definitions Section, later in this document.

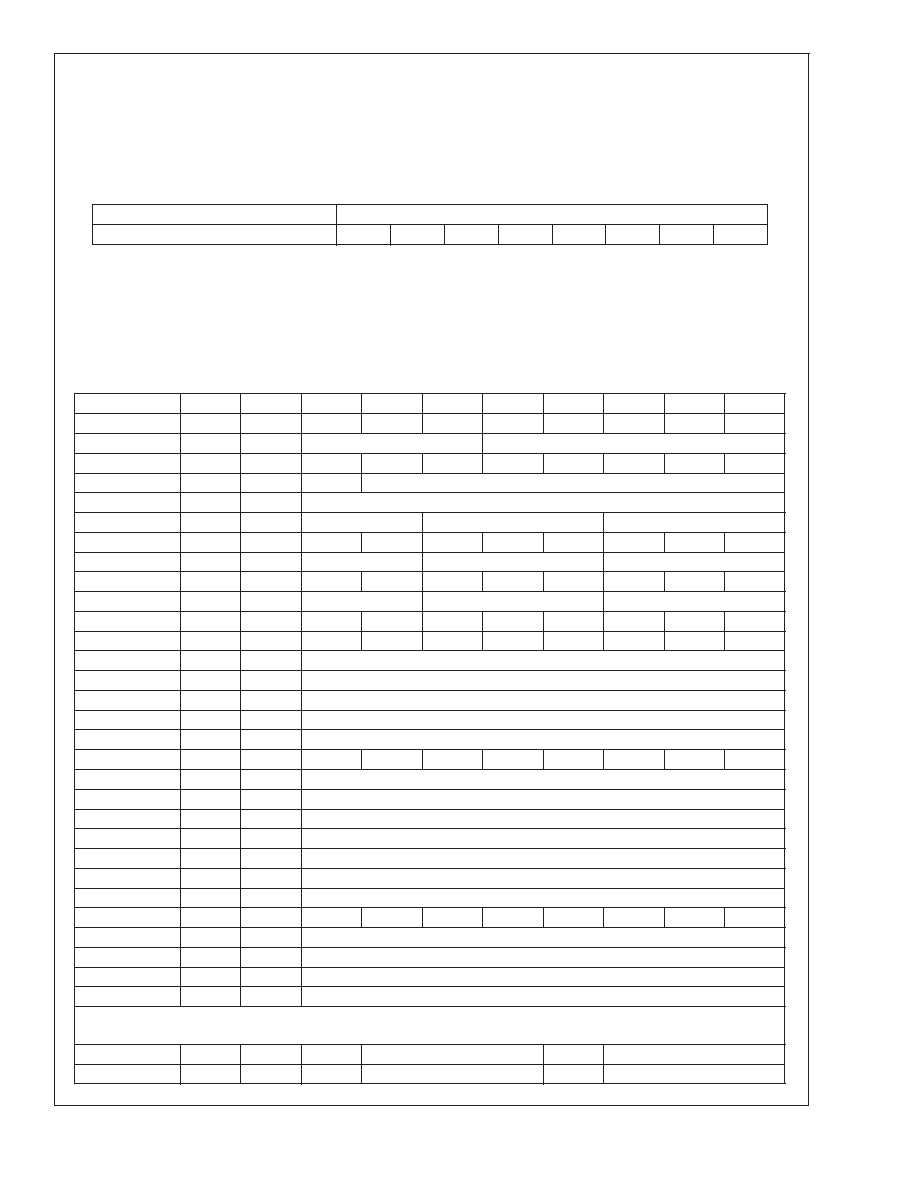

TABLE 14. OSD Control Register Detail

Register

Address

Default

D7

D6

D5

D4

D3

D2

D1

D0

FRMCTRL1

0x8400

0x10

X

TD

CDPR

D2E

D1E

OSE

FRMCTRL2

0x8401

0x80

PIXELS_PER_LINE[2:0]

BLINK_PERIOD[4:0]

CHARFONTACC

0x8402

0x00

XXXXXX

ATTR

FONT4

VBLANKDUR

0x8403

0x10

X

VBLANK_DURATION[6:0]

CHARHTCTRL

0x8404

0x51

CHAR_HEIGHT[7:0]

BBHLCTRLB0

0x8405

0xFF

B[1:0]

G[2:0]

R[2:0]

BBHLCTRLB1

0x8406

0x01

XXXXXXX

B[2]

BBLLCTRLB0

0x8407

0x00

B[1:0]

G[2:0]

R[2:0]

BBLLCTRLB1

0x8408

0x00

XXXXXXX

B[2]

CHSDWCTRLB0

0x8409

0x00

B[1:0]

G[2:0]

R[2:0]

CHSDWCTRLB1

0x840A

0x00

XXXXXXX

B[2]

ROMSIGCTRL

0x840D

0x00

XXXXXXX

CRS

ROMSIGDATAB0

0x840E

0x00

CRC[7:0]

ROMSIGDATAB1

0x840F

0x00

CRC[15:8]

HSTRT1

0x8410

0x13

HPOS[7:0]

VSTRT1

0x8411

0x14

VPOS[7:0]

W1STRTADRL

0x8412

0x00

ADDR[7:0]

W1STRTADRH

0x8413

0x00

XXXXXXX

ADDR[8]

COLWIDTH1B0

0x8414

0x00

COL[7:0]

COLWIDTH1B1

0x8415

0x00

COL[15:8]

COLWIDTH1B2

0x8416

0x00

COL[23:16]

COLWIDTH1B3

0x8417

0x00

COL[31:24]

HSTRT2

0x8418

0x56

HPOS[7:0]

VSTRT2

0x8419

0x5B

VPOS[7:0]

W2STRTADRL

0x841A

0x00

ADDR[7:0]

W2STRTADRH

0x841B

0x01

XXXXXXX

ADDR[8]

COLWIDTH2B0

0x841C

0x00

COL[7:0]

COLWIDTH2B1

0x841D

0x00

COL[15:8]

COLWIDTH2B2

0x841E

0x00

COL[23:16]

COLWIDTH2B3

0x841F

0x00

COL[31:24]

Any registers in the range of 0x8420 - 0x8426 are for National Semiconductor internal use only and should not be written to

under application conditions.

BANKSEL_0-1

0x8427

0x10

X

B1AD[2:0]

X

B0AD[2:0]

BANKSEL_2-3

0x8428

0x32

X

B3AD[2:0]

X

B2AD[2:0]

LM1247

www.national.com

25

相关PDF资料 |

PDF描述 |

|---|---|

| LM1253AAE/NA | ON-SCREEN DISPLAY IC, PDIP28 |

| LM1267NA/NOPB | 3 CHANNEL, VIDEO PREAMPLIFIER, PDIP24 |

| LM1269NA/NOPB | 3 CHANNEL, VIDEO PREAMPLIFIER, PDIP24 |

| LM1276AAA/NA | 1 CHANNEL, VIDEO PREAMPLIFIER, PDIP28 |

| LM1279AN/NOPB | 3 CHANNEL, VIDEO AMPLIFIER, PDIP20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LM1247DMC/NA | 制造商:Texas Instruments 功能描述: |

| LM124A | 制造商:NSC 制造商全称:National Semiconductor 功能描述:Low Power Quad Operational Amplifiers |

| LM124AD | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:LOW POWER QUAD OPERATIONAL AMPLIFIERS |

| LM124ADR | 制造商:TI 制造商全称:Texas Instruments 功能描述:QUADRUPLE OPERATIONAL AMPLIFIERS |

| LM124ADT | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Voltage-Feedback Operational Amplifier |

发布紧急采购,3分钟左右您将得到回复。