- 您现在的位置:买卖IC网 > PDF目录358886 > LMX2353TMX (NATIONAL SEMICONDUCTOR CORP) PLLatinum⑩ Fractional N Single 2.5 GHz Frequency Synthesizer PDF资料下载

参数资料

| 型号: | LMX2353TMX |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | XO, clock |

| 英文描述: | PLLatinum⑩ Fractional N Single 2.5 GHz Frequency Synthesizer |

| 中文描述: | PHASE LOCKED LOOP, 2500 MHz, PDSO16 |

| 封装: | PLASTIC, TSSOP-16 |

| 文件页数: | 11/16页 |

| 文件大小: | 210K |

| 代理商: | LMX2353TMX |

2.0 Programming Description

(Continued)

R:

P:

Preset divide ratio of binary 15-bit programmable reference counter (3 to 32767)

Preset modulus of dual modulus prescaler (P = 16 or 32)

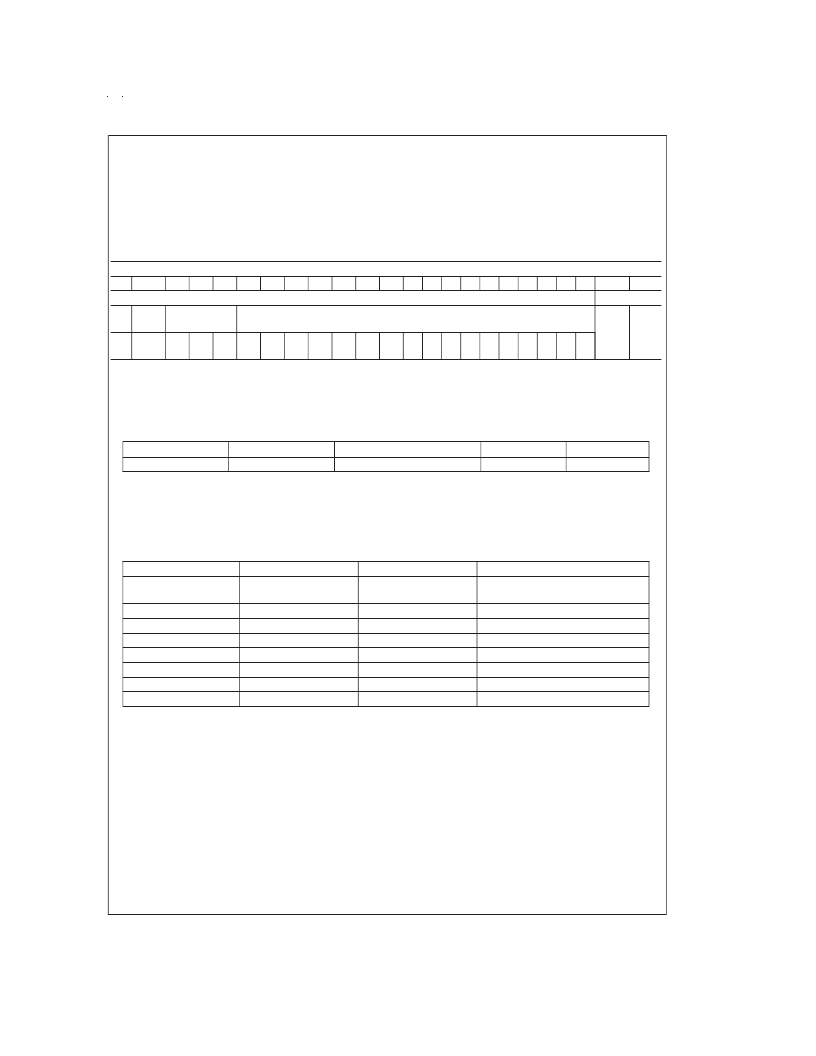

2.4 F1 REGISTER

If theADDRESS[1:0] field is set to 0 0, data is transferred from the 24-bit shift register into the F1 register when Latch Enable (LE)

signal goes high . The F1 register sets the fractional divider denominator FRAC_16 bit and F

out

/ Lock Dectect output F

o

LD word.

The rest of the bits F1_0 - F1_16, and F1_21 are Don’t Care.

Most Significant Bit

23

22

SHIFT REGISTER BIT LOCATION

14

13

12

11

Data Field

Least Significant Bit

3

2

Address Field

21

20

19

18

17

16

15

10

9

8

7

6

5

4

1

0

0

FRAC

_16

F1

_20

F

o

LD

These bits should be set to zero

0

0

F1

_21

F1

_19

F1

_18

F1

_17

F1

_16

F1

_15

F1

_14

F1

_13

F1

_12

F1

_11

F1

_10

F1

_9

F1

_8

F1

_7

F1

_6

F1

_5

F1

_4

F1

_3

F1

_2

F1

_1

F1

_0

Note:

0 denotes setting the bit to zero.

2.4.1 FRAC_16

The FRAC_16 bit is used to set the fractional compensation at either 1/16 or 1/15 resolution. When FRAC_16 bit is set to one,

the fractional modulus is set to 1/16 resolution, and FRAC_16 = 0 corresponds to 1/15. See section 2.3.5 for fractional divider

values.

Bit

Location

F1_20

Function

0

1

FRAC_16

Fractional Modulus

1/15

1/16

2.4.2 F

o

LD

The F

LD word is used to set the function of the Lock Detect output pin according to the Table 2.4.2.1 below. Open drain lock de-

tect output is provided to indicate when the VCO frequency is in “lock”. When the loop is locked and a lock detect mode is se-

lected, the pin is HIGH, with narrow pulses LOW. See typical Lock detect timing in section 2.4.2.4.

2.4.2.1 F

O

LD Programming Truth Table

F1_19

0

F1_18

0

F1_17

0

F

o

LD Output State

Analog Lock Detect

(Open Drain)

Reserved

Digital Lock Detect

Reserved

Reserved

Reserved

N Divider Output

R Divider Output

0

0

0

1

1

1

1

0

1

1

0

0

1

1

1

0

1

0

1

0

1

Reserved - Denotes a disallowed programming condition.

2.4.2.2 Lock Detect (LD) Digital Filter

The LD Digital Filter compares the difference between the phase of the inputs of the phase detector to a RC generated delay of

approximately 15 ns. To enter the locked state (Lock = HIGH) the phase error must be less than the 15 ns RC delay for 5 con-

secutive reference cycles. Once in lock (Lock = HIGH), the RC delay is changed to approximately 30 ns. To exit the locked state

(Lock = LOW), the phase error must become greater than the 30 ns RC delay. If the PLL is unlocked, the lock detect output will

be forced LOW. A flow chart of the digital filter is shown next.

www.national.com

11

相关PDF资料 |

PDF描述 |

|---|---|

| LMX2353TM | PLLatinum⑩ Fractional N Single 2.5 GHz Frequency Synthesizer |

| LMX2353SLBX | PLLatinum⑩ Fractional N Single 2.5 GHz Frequency Synthesizer |

| LMX2353 | PLLatinum⑩ Fractional N Single 2.5 GHz Frequency Synthesizer |

| LMX2372 | PLLatinum⑩ Dual Frequency Synthesizer for RF Personal Communications |

| LMX2372SLBX | PLLatinum⑩ Dual Frequency Synthesizer for RF Personal Communications |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LMX2353TMX/NOPB | 功能描述:IC FREQ SYNTH 2.5GHZ 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| LMX2354 | 制造商:NSC 制造商全称:National Semiconductor 功能描述:PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2354SLB | 制造商:NSC 制造商全称:National Semiconductor 功能描述:PLLatinum Fractional N RF/ Integer N IF Dual Low Power Frequency Synthesizer |

| LMX2354SLBX | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| LMX2354SLBX/NOPB | 功能描述:IC FREQ SYNTH DUAL 24-LAMCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。