- 您现在的位置:买卖IC网 > PDF目录10533 > LTC2251CUH#PBF (Linear Technology)IC ADC 10-BIT 125MSPS 3V 32-QFN PDF资料下载

参数资料

| 型号: | LTC2251CUH#PBF |

| 厂商: | Linear Technology |

| 文件页数: | 8/24页 |

| 文件大小: | 0K |

| 描述: | IC ADC 10-BIT 125MSPS 3V 32-QFN |

| 标准包装: | 73 |

| 位数: | 10 |

| 采样率(每秒): | 125M |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 468mW |

| 电压电源: | 单电源 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-WFQFN 裸露焊盘 |

| 供应商设备封装: | 32-QFN 裸露焊盘(5x5) |

| 包装: | 管件 |

| 输入数目和类型: | 1 个单端,双极; 1 个差分,双极 |

| 产品目录页面: | 1349 (CN2011-ZH PDF) |

LTC2251/LTC2250

16

22510fa

APPLICATIO S I FOR ATIO

WU

UU

The difference amplifier generates the high and low refer-

ence for the ADC. High speed switching circuits are

connected to these outputs and they must be externally

bypassed. Each output has two pins. The multiple output

pins are needed to reduce package inductance. Bypass

capacitors must be connected as shown in Figure 9.

Other voltage ranges in-between the pin selectable ranges

can be programmed with two external resistors as shown

in Figure 10. An external reference can be used by applying

its output directly or through a resistor divider to SENSE.

It is not recommended to drive the SENSE pin with a logic

device. The SENSE pin should be tied to the appropriate

level as close to the converter as possible. If the SENSE pin

is driven externally, it should be bypassed to ground as

close to the device as possible with a 1

Fceramiccapacitor.

VCM

SENSE

1.5V

0.75V

2.2

F

12k

1

F

12k

22510 F10

LTC2251/

LTC2250

Figure 10. 1.5V Range ADC

In applications where jitter is critical, such as when digitiz-

ing high input frequencies, use as large an amplitude as

possible. Also, if the ADC is clocked with a sinusoidal

signal, filter the CLK signal to reduce wideband noise and

distortion products generated by the source.

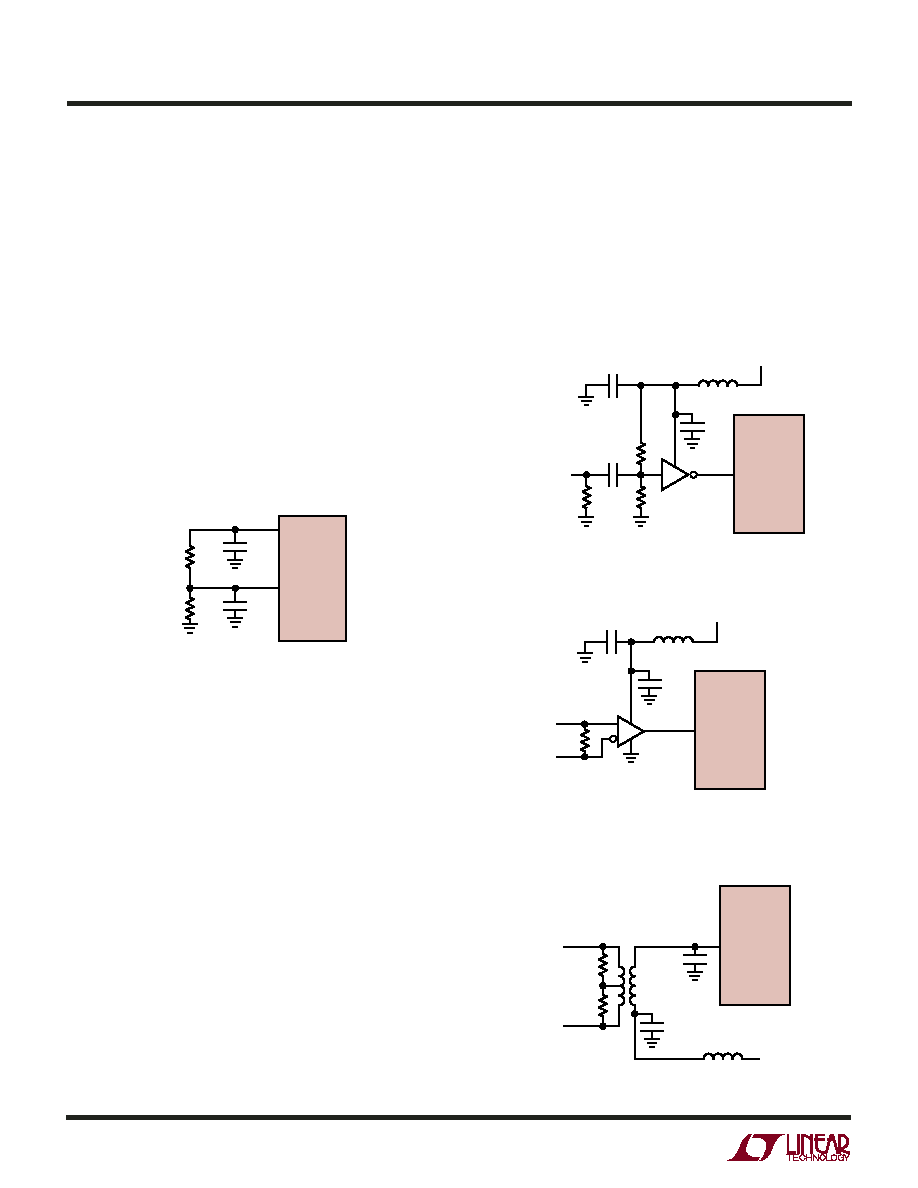

Figures 12 and 13 show alternatives for converting a

differential clock to the single-ended CLK input. The use of

Input Range

The input range can be set based on the application. The

2V input range will provide the best signal-to-noise perfor-

mance while maintaining excellent SFDR. The 1V input

range will have better SFDR performance, but the SNR will

degrade by 0.9dB.

Driving the Clock Input

The CLK input can be driven directly with a CMOS or TTL

level signal. A sinusoidal clock can also be used along with

a low-jitter squaring circuit before the CLK pin (see

Figure 11).

The noise performance of the LTC2251/LTC2250 can

depend on the clock signal quality as much as on the

analog input. Any noise present on the clock signal will

result in additional aperture jitter that will be RMS summed

with the inherent ADC aperture jitter.

Figure 11. Sinusoidal Single-Ended CLK Drive

CLK

50

0.1

F

0.1

F

4.7

F

1k

FERRITE

BEAD

CLEAN

SUPPLY

SINUSOIDAL

CLOCK

INPUT

22510 F11

NC7SVU04

LTC2251/

LTC2250

CLK

100

0.1

F

4.7

F

FERRITE

BEAD

CLEAN

SUPPLY

IF LVDS USE FIN1002 OR FIN1018.

FOR PECL, USE AZ1000ELT21 OR SIMILAR

22510 F12

LTC2251/

LTC2250

CLK

5pF-30pF

ETC1-1T

0.1

F

VCM

FERRITE

BEAD

DIFFERENTIAL

CLOCK

INPUT

22510 F13

LTC2251/

LTC2250

Figure 12. CLK Drive Using an LVDS or PECL to CMOS Converter

Figure 13. LVDS or PECL CLK Drive Using a Transformer

相关PDF资料 |

PDF描述 |

|---|---|

| UMK105CH180KW-F | CAP CER 18PF 50V 10% C0H 0402 |

| MS3102A18-9S | CONN RCPT 7POS BOX MNT W/SCKT |

| PT07E-10-6S | CONN RCPT 6 POS JAM NUT W/SCKT |

| ISL3232EIRZ-T7A | IC XMITTER/RCVR ESD RS232 16QFN |

| TPA3130D2DAP | IC AMP AUD PWR 15W STER 32HTSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC2251IUH | 制造商:LINER 制造商全称:Linear Technology 功能描述:10-Bit, 125/105Msps Low Noise 3V ADCs |

| LTC2251IUH#PBF | 功能描述:IC ADC 10-BIT 125MSPS 3V 32-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1 系列:- 位数:14 采样率(每秒):83k 数据接口:串行,并联 转换器数目:1 功率耗散(最大):95mW 电压电源:双 ± 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:28-DIP(0.600",15.24mm) 供应商设备封装:28-PDIP 包装:管件 输入数目和类型:1 个单端,双极 |

| LTC2251IUH#TRPBF | 功能描述:IC ADC 10BIT 125MSPS 3V 32-QFN RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:12 采样率(每秒):300k 数据接口:并联 转换器数目:1 功率耗散(最大):75mW 电压电源:单电源 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:24-SOIC(0.295",7.50mm 宽) 供应商设备封装:24-SOIC 包装:带卷 (TR) 输入数目和类型:1 个单端,单极;1 个单端,双极 |

| LTC2252 | 制造商:LINER 制造商全称:Linear Technology 功能描述:14-Bit, 125/105Msps Low Power 3V ADCs |

| LTC2252CUH | 制造商:Linear Technology 功能描述:Single ADC Pipelined 105Msps 12-bit Parallel 32-Pin QFN EP |

发布紧急采购,3分钟左右您将得到回复。