- 您现在的位置:买卖IC网 > PDF目录39416 > LTC2272IUJ#TR (LINEAR TECHNOLOGY CORP) 1-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PQCC40 PDF资料下载

参数资料

| 型号: | LTC2272IUJ#TR |

| 厂商: | LINEAR TECHNOLOGY CORP |

| 元件分类: | ADC |

| 英文描述: | 1-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PQCC40 |

| 封装: | 6 X 6 MM, PLASTIC, QFN-40 |

| 文件页数: | 15/44页 |

| 文件大小: | 767K |

| 代理商: | LTC2272IUJ#TR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

LTC2273/LTC2272

22

22732fa

APPLICATIONS INFORMATION

SAMPLE/HOLD OPERATION AND INPUT DRIVE

Sample/Hold Operation

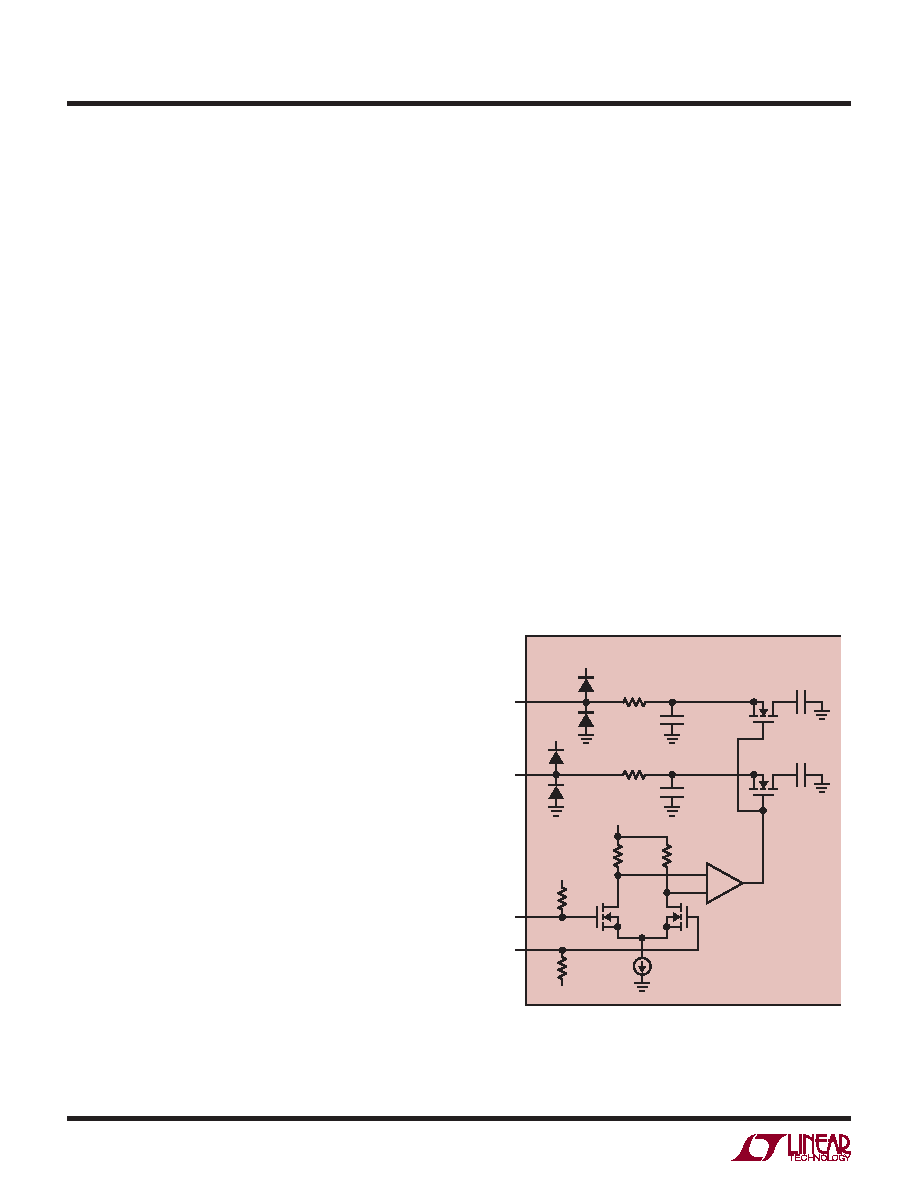

Figure 2 shows an equivalent circuit for the LTC2273/

LTC2272 CMOS differential sample and hold. The differ-

ential analog inputs are sampled directly onto sampling

capacitors (CSAMPLE) through NMOS transistors. The

capacitors shown attached to each input (CPARASITIC) are

the summation of all other capacitance associated with

each input.

During the sample phase when ENC is low, the NMOS

transistors connect the analog inputs to the sampling

capacitors and they charge to, and track, the differential

input voltage. On the rising edge of ENC, the sampled

input voltage is held on the sampling capacitors. During

the hold phase when ENC is high, the sampling capacitors

are disconnected from the input and the held voltage is

passed to the ADC core for processing. As ENC transitions

for high to low, the inputs are reconnected to the sampling

capacitors to acquire a new sample. Since the sampling

capacitors still hold the previous sample, a charging glitch

proportional to the change in voltage between samples will

be seen at this time. If the change between the last sample

and the new sample is small, the charging glitch seen at

the input will be small. If the input change is large, such

as the change seen with input frequencies near Nyquist,

then a larger charging glitch will be seen.

Common Mode Bias

The ADC sample-and-hold circuit requires differential drive

to achieve specied performance. Each input should swing

±0.5625V for the 2.25V range (PGA = 0) or ±0.375V for

the 1.5V range (PGA = 1), around a common mode volt-

age of 1.25V. The VCM output pin (Pin 39) is designed to

provide the common mode bias level. VCM can be tied

directly to the center tap of a transformer to set the DC

input level or as a reference level to an op amp differential

driver circuit. The VCM pin must be bypassed to ground

close to the ADC with 2.2μF or greater.

Input Drive Impedance

As with all high performance, high speed ADCs the

dynamic performance of the LTC2273/LTC2272 can be

inuenced by the input drive circuitry, particularly the

second and third harmonics. Source impedance and in-

put reactance can inuence SFDR. At the falling edge of

ENC the sample-and-hold circuit will connect the 4.9pF

sampling capacitor to the input pin and start the sampling

period. The sampling period ends when ENC rises, hold-

ing the sampled input on the sampling capacitor. Ideally,

the input circuitry should be fast enough to fully charge

the sampling capacitor during the sampling period

1/(2FENCODE); however, this is not always possible and the

incomplete settling may degrade the SFDR. The sampling

glitch has been designed to be as linear as possible to

minimize the effects of incomplete settling.

For the best performance it is recommended to have a

source impedance of 100

Ω or less for each input. The

source impedance should be matched for the differential

inputs. Poor matching will result in higher even order

harmonics, especially the second.

CSAMPLE

4.9pF

VDD

LTC2273/LTC2272

AIN+

22732 F02

CSAMPLE

4.9pF

VDD

AIN–

ENC–

ENC+

1.6V

6k

1.6V

6k

CPARASITIC

1.8pF

CPARASITIC

1.8pF

RPARASITIC

3Ω

RON

20Ω

RON

20Ω

RPARASITIC

3Ω

Figure 2. Equivalent Input Circuit

相关PDF资料 |

PDF描述 |

|---|---|

| LTC2273IUJ#TR | 1-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PQCC40 |

| LTC2273IUJ | 1-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PQCC40 |

| LTC2274CUJ#TR | 1-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PQCC40 |

| LTC2274CUJ | 1-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PQCC40 |

| LTC2274IUJ#TR | 1-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PQCC40 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC2272IUJ-TRPBF | 制造商:LINER 制造商全称:Linear Technology 功能描述:16-Bit, 80Msps/65Msps Serial Output ADC |

| LTC2272UJ | 制造商:LINER 制造商全称:Linear Technology 功能描述:16-Bit, 80Msps/65Msps Serial Output ADC |

| LTC2273 | 制造商:LINER 制造商全称:Linear Technology 功能描述:16-Bit, 80Msps/65Msps Serial Output ADC |

| LTC2273CUJ | 制造商:LINER 制造商全称:Linear Technology 功能描述:16-Bit, 80Msps/65Msps Serial Output ADC |

| LTC2273CUJ#PBF | 制造商:Linear Technology 功能描述:IC ADC 16BIT 80MSPS 40-QFN 制造商:Linear Technology 功能描述:IC ADC 16BIT 80MSPS QFN-40 制造商:Linear Technology 功能描述:IC, ADC, 16BIT, 80MSPS, QFN-40, Resolution (Bits):16bit, Sampling Rate:80MSPS, Supply Voltage Type:Single, Supply Voltage Min:3.135V, Supply Voltage Max:3.465V, Supply Current:233mA, Digital IC Case Style:QFN, No. of Pins:40 , RoHS Compliant: Yes 制造商:Linear Technology 功能描述:MS-ADC/High Speed, 16-bit, 80Msps Serial ADC |

发布紧急采购,3分钟左右您将得到回复。