- 您现在的位置:买卖IC网 > PDF目录19912 > LTC4252-2IMS8#PBF (Linear Technology)IC CNTRLR HOTSWAP NEGVOLT 8-MSOP PDF资料下载

参数资料

| 型号: | LTC4252-2IMS8#PBF |

| 厂商: | Linear Technology |

| 文件页数: | 24/36页 |

| 文件大小: | 328K |

| 描述: | IC CNTRLR HOTSWAP NEGVOLT 8-MSOP |

| 标准包装: | 50 |

| 类型: | 热交换控制器 |

| 应用: | 通用 |

| 内部开关: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-TSSOP,8-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 8-MSOP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

LTC4252-1/LTC4252-2

LTC4252A-1/LTC4252A-2

24

425212fe

For more information www.linear.com/LTC4252-1

applicaTions inForMaTion

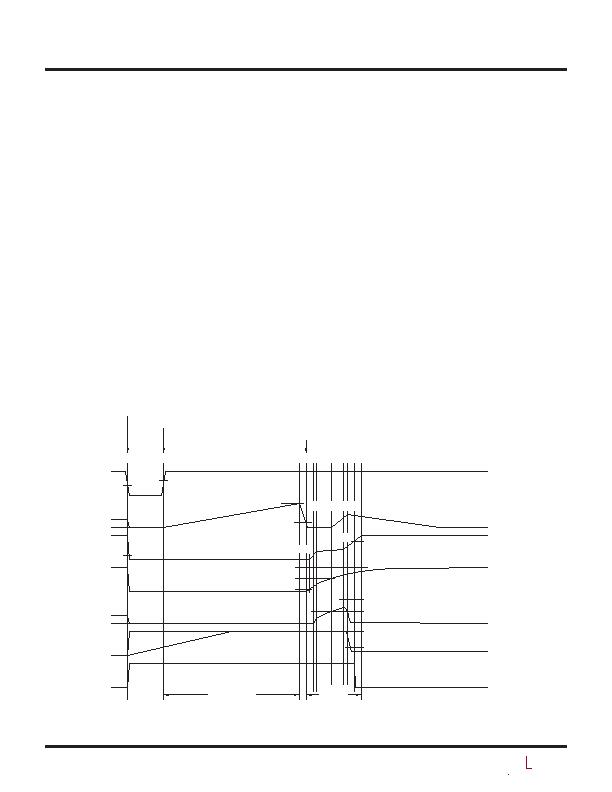

Undervoltage Timing

In Figure 11 when UV pin drops below V

UVLO

(time point?),

the LTC4252 shuts down with TIMER, SS and GATE all

pulling low. If current has been flowing, the SENSE pin

voltage decreases to zero as GATE collapses. When UV

recovers and clears V

UVHI

(time point 2), an initial timer

cycle begins followed by a GATE start-up cycle.

V

IN

Undervoltage Lockout Timing

The V

IN

undervoltage lockout comparator, UVLO, has a

similar timing behavior as the UV pin timing except it looks

for V

IN

< (V

LKO

V

LKH

) to shut down and V

IN

> V

LKO

to

start. In an undervoltage lockout condition, both UV and

OV comparators are held off. When V

IN

exits undervoltage

lockout, the UV and OV comparators are enabled.

Undervoltage Timing with Overvoltage Glitch

In Figure 12, both UV and OV pins are connected together.

When UV clears V

UVHI

(time point 1), an initial timing

cycle starts. If the system bus voltage overshoots V

OVHI

as shown at time point 2, TIMER discharges. At time point

3, the supply voltage recovers and drops below the V

OVLO

threshold. The initial timing cycle restarts, followed by a

GATE start-up cycle.

Overvoltage Timing

During normal operation, if the OV pin exceeds V

OVHI

as

shown at time point 1 of Figure 13, the TIMER and PWRGD

status are unaffected. Nevertheless, SS and GATE pull down

and the load is disconnected. At time point 2, OV recovers

and drops below the V

OVLO

threshold. A GATE start-up

cycle begins. If the overvoltage glitch is long enough to

deplete the load capacitor, a full start-up cycle as shown

between time points 4 through 7 may occur.

Circuit Breaker Timing

In Figure 14a, the TIMER capacitor charges at 230礎 if

the SENSE pin exceeds V

CB

but V

DRN

is less than 5V . If

the SENSE pin drops below V

CB

before TIMER reaches

UV

TIMER

GATE

SENSE

SS

DRAIN

PWRGD

5.8礎

58礎

5.8礎

5.8礎

58礎

UV DROPS BELOW V

UVLO

. GATE, SS AND TIMER ARE PULLED DOWN, PWRGD RELEASES

1

2

3 4 56 7 89

TIMER CLEARS V

TMRL

, CHECK GATE < V

GATEL

, SENSE < V

CB

AND SS < 20 " V

OS

1011

425212 F11

UV CLEARS V

UVHI

, CHECK OV CONDITION, GATE < V

GATEL

, SENSE < V

CB

, SS < 20 " V

OS

AND TIMER < V

TMRL

V

ACL

V

CB

230礎 + 8 " I

DRN

20 " V

OS

V

IN

V

GATEH

V

DRNL

V

DRNCL

20 " (V

CB

+ V

OS

)

20 " (V

ACL

+ V

OS

)

V

GATEL

V

TMRL

V

TMRH

V

UVHI

V

UVLO

GATE

START-UP

INITIAL TIMING

Figure 11. Undervoltage Timing (All Waveforms Are Referenced to V

EE

)

相关PDF资料 |

PDF描述 |

|---|---|

| GRM2165C2A131JA01D | CAP CER 130PF 100V 5% NP0 0805 |

| RCB92DHRR-S378 | EDGECARD EXT PCI64 184PS .050 5V |

| ECC13DREH-S13 | CONN EDGECARD 26POS .100 EXTEND |

| NCV59301DS28R4G | IC REG LDO 2.8V 3A D2PAK-5 |

| TACA336M010XTA | CAP TANT 33UF 10V 20% 1206 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC4252-2IMS8TR | 制造商:LINER 制造商全称:Linear Technology 功能描述:Negative Voltage Hot Swap Controllers |

| LTC4252-2IMS8TRPBF | 制造商:LINER 制造商全称:Linear Technology 功能描述:Negative Voltage Hot Swap Controllers |

| LTC4252-2IMSPBF | 制造商:Linear Technology 功能描述:Hot Swap Controller 1-Channel MSOP10 |

| LTC4252-2IMSTR | 制造商:LINER 制造商全称:Linear Technology 功能描述:Negative Voltage Hot Swap Controllers |

| LTC4252-2IMSTRPBF | 制造商:LINER 制造商全称:Linear Technology 功能描述:Negative Voltage Hot Swap Controllers |

发布紧急采购,3分钟左右您将得到回复。