- 您现在的位置:买卖IC网 > PDF目录180046 > LUCL9219GAR-DT Low-Cost Line Interface with Reverse Battery and Dual Current Limit PDF资料下载

参数资料

| 型号: | LUCL9219GAR-DT |

| 英文描述: | Low-Cost Line Interface with Reverse Battery and Dual Current Limit |

| 中文描述: | 低成本线接口,具有反向电池和双电流限制 |

| 文件页数: | 30/30页 |

| 文件大小: | 397K |

| 代理商: | LUCL9219GAR-DT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页

Agere Systems Inc.

9

Data Sheet

November 2001

with Reverse Battery and Dual Current Limit

L9219A/G Low-Cost Line Interface

Electrical Characteristics (continued)

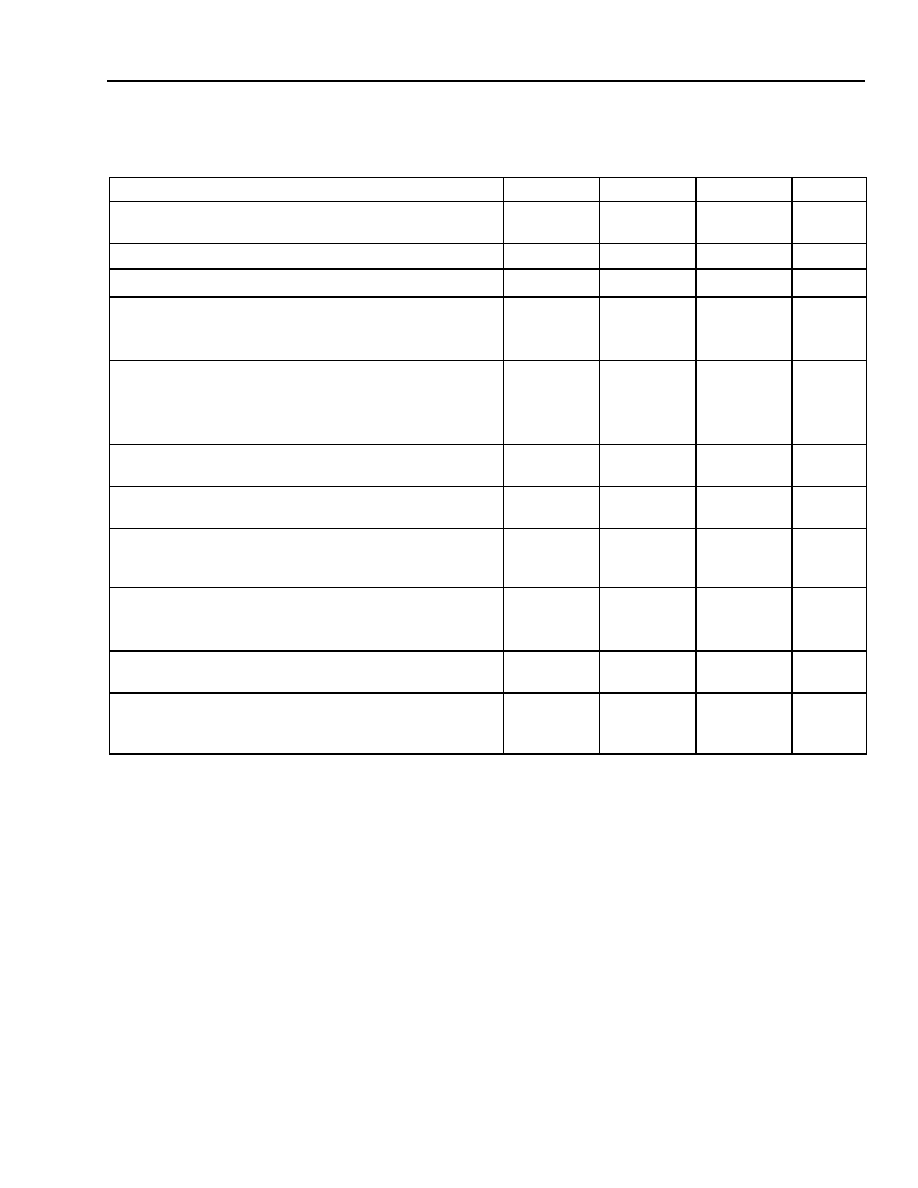

Table 5. 2-Wire Port

1. The longitudinal current is independent of dc loop current.

2. Current-limit ILIM is programmed by a resistor, RPROG, from pin IPROG to DCOUT. ILIM is specified at the loop resistance where current limiting

begins (see Figure 13).

3. This parameter is not tested in production. It is guaranteed by design and device characterization.

4. Specification is reduced to |VBAT1 + 10.5 V| minimum when VBAT1 = –70 V at 85

°C.

5. Longitudinal balance of circuit card will depend on loop series protection resistor matching and magnitude. More information is available in

the Applications section of this document.

Parameter

Min

Typ

Max

Unit

Tip or Ring Drive Current = dc + Longitudinal + Signal

Currents

80

—

mA

Signal Current

15

—

mArms

Longitudinal Current Capability per Wire1

8.5

15

—

mArms

dc Loop Current Limit2:

Allowed Range Including Tolerance3

Accuracy (RLOOP = 100

, VBAT = –48 V)

15

—

±5

45

—

mA

%

Powerup Open Loop Voltage Levels:

Common-mode Voltage

Differential Voltage VBAT = –48 V4 (Gain = 2)

Differential Voltage VBAT = –48 V4 (Gain = 7.86)

—

|VBAT + 7.5|

|VBAT + 8.0|

VBAT/2

|VBAT + 6.5|

—

|VBAT + 5.9|

V

Disconnect State:

Leakage

—

10

150

A

dc Feed Resistance (for ILOOP below regulation level) (does

not include protection resistor)

—

70

100

Loop Resistance Range (–3.17 dBm overload into

900

; not including protection):

ILOOP = 20 mA at VBAT = –48 V

1800

—

Longitudinal to Metallic Balance—

IEEE Std. 455

(See Figure 7)5:

200 Hz to 3400 Hz

58

61

—

dB

Metallic to Longitudinal Balance (open loop):

200 Hz to 4 kHz

40

—

dB

RFI Rejection (See Figure 8)3, 0.5 Vrms, 50

Source,

30% AM Mod 1 kHz:

500 kHz to 100 MHz

—

–55

—

–45

—

dBV

相关PDF资料 |

PDF描述 |

|---|---|

| LUPXA255A0C200 | 32-BIT, 200 MHz, MICROPROCESSOR, PBGA256 |

| LUPXA255A0C300 | 32-BIT, 300 MHz, MICROPROCESSOR, PBGA256 |

| LV100 | Voltage Transducer LV 100 |

| LV200-AW | Voltage Transducer LV 200-AW/2 |

| LV25-1000 | Voltage Transducer LV 25-1000 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LUCL9310AP-D | 制造商:AGERE 制造商全称:AGERE 功能描述:Line Interface and Line Access Circuit Full-Feature SLIC,Ringing Relay,and Test Access Device |

| LUCL9310AP-DT | 制造商:AGERE 制造商全称:AGERE 功能描述:Line Interface and Line Access Circuit Full-Feature SLIC,Ringing Relay,and Test Access Device |

| LUCL9310GP-D | 制造商:AGERE 制造商全称:AGERE 功能描述:Line Interface and Line Access Circuit Full-Feature SLIC,Ringing Relay,and Test Access Device |

| LUCL9310GP-DT | 制造商:AGERE 制造商全称:AGERE 功能描述:Line Interface and Line Access Circuit Full-Feature SLIC,Ringing Relay,and Test Access Device |

| LUCL9311AP-D | 制造商:AGERE 制造商全称:AGERE 功能描述:Line Interface and Line Access Circuit Full-Feature SLIC with High Longitudinal Balance, Ringing Relay,and GR-909 Test Access |

发布紧急采购,3分钟左右您将得到回复。