- 您现在的位置:买卖IC网 > PDF目录67759 > LX1801CLQ (MICROSEMI CORP) SPECIALTY ANALOG CIRCUIT, PQCC16 PDF资料下载

参数资料

| 型号: | LX1801CLQ |

| 厂商: | MICROSEMI CORP |

| 元件分类: | 模拟信号调理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQCC16 |

| 封装: | 3 X 3 MM, ROHS COMPLIANT, PLASTIC, MLPQ-16 |

| 文件页数: | 6/12页 |

| 文件大小: | 255K |

| 代理商: | LX1801CLQ |

LX1801

PRODUCTION DATA SHEET

Microsemi

Integrated Products Division

11861 Western Avenue, Garden Grove, CA. 92841, 714-898-8121, Fax: 714-893-2570

Page 3

Copyright

2005

Rev. 1.0, 5/4/2006

WWW

.Microse

m

i

.CO

M

SMBus to Analog & Digital System Interface

TM

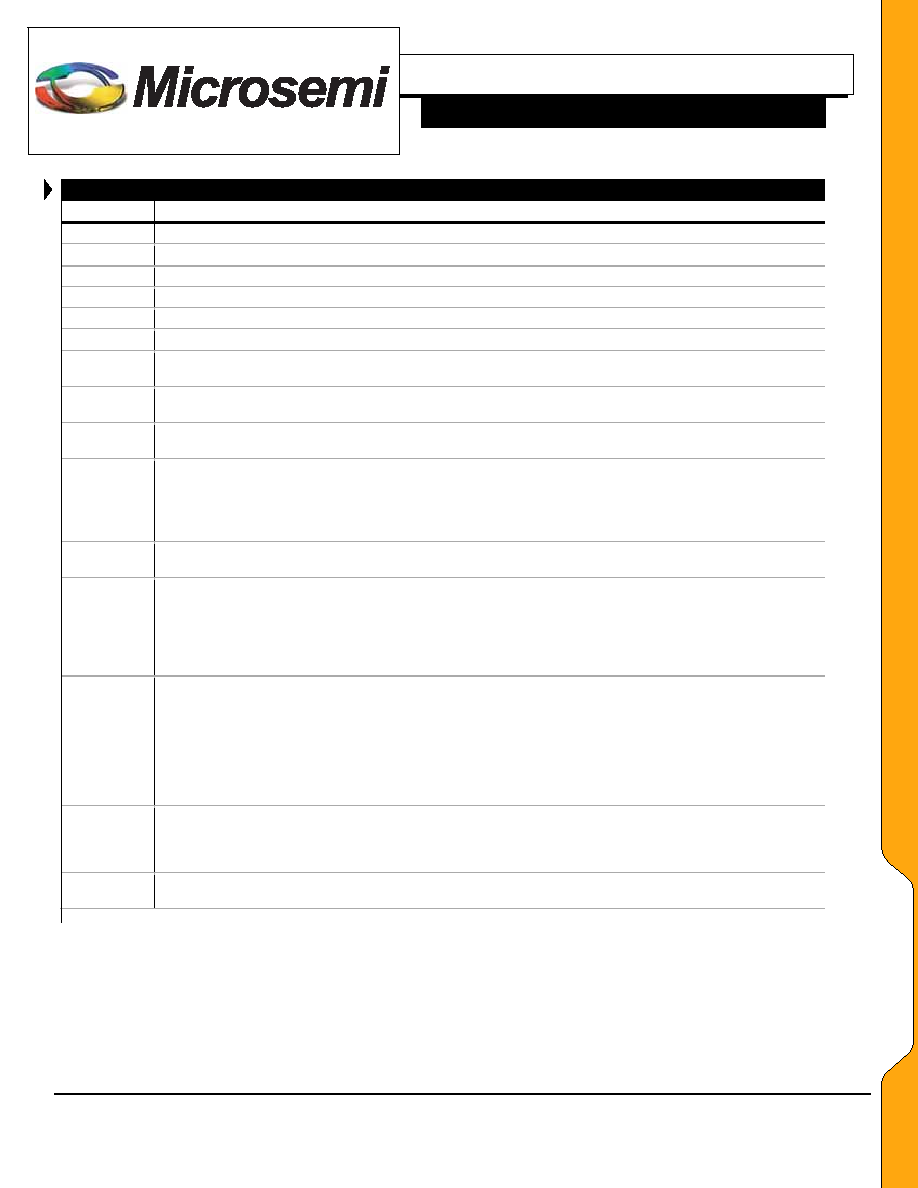

FUNCTIONAL PIN DESCRIPTION

Name

Description

VDD

Power Supply Input: 4.5V to 5.5V

VSS

Ground (2 Pins)

SCL

Digital Input. SMBus Clock – 10 to 100 KHz capable

SDA

Digital I/O. SMBus Data – SMBus Data line

ADR0

SMBus Address strap input – The address for the LX1801 is determined by the state of this pin (see table 1).

ALS_IN

Analog input. Ambient light sensor input. Zero to VREF_IN range.

PWM_IN

A digital input from the system controller whose duty cycle determines lamp brightness when in PWM mode,

and multiplies lamp brightness by a fractional value equal to its duty cycle when in DPST mode.

VREF_IN

Analog Input reference voltage for ADC and DAC. Operating range is 1.5 to 3 Vdc. Nominal input is 2.040V.

Input impedance is greater than 10M.

V_BOT

An analog voltage input whose value determines the minimum output voltage of BRITE_OUT after the effect

of the PWM input when in DPST mode and at all times in other modes.

BRITE_OUT

Analog output voltage that is equal to desired BRITE_OUT voltage after modulation by the PWM input and

offset by the voltage at the V_BOT input. An R/C filter at this pin to low pass filters the signal and determines

response time when in PWM and DPST modes. In PWM and DPST modes, the output voltage is modulated

on and off at the duty cycle and frequency of PWM_IN. The R/C filter is comprised of an internal 100K

resistor and an external capacitor to ground.

LMP_C

Lamp Capacitor. A capacitor, typically 10nF and a resistor, typically 1M, are connected in parallel from

this pin to ground. They filter a peak voltage detector with the LMP_ON input.

OVR_CUR

Analog / Digital input to comparator and latch. Used for over current status input in M07 application. 1.2V

threshold. If OVR_CUR > 1.2VDC, a “1” is latched and written to bit 0 (FAULT) and bit 2(OV_CURR) of the

fault status register (Register 0x02). The latched bits can only be cleared by a write byte command to

register 0x01 to make the LAMP_CTL bit true. If bit 0 or bit 2 of register 0x02 is set, this will reset the

LAMP_CTL bit in register 0x01, causing the enable output to the CCFL controller (EN_OUT) to go low and

turn off the inverter. Zero to VDD input voltage range.

LMP_ON

Digital input. Approximately 1V threshold. When LMP_ON is “1” it charges the capacitor at pin LMP_C to

VDD, indicating the lamp is turned on. This pin is normally connected to the A_OUT pin of the LX1692 / 93

controller, and will cause internal circuitry to report the lamp is on if there are pulses on A_OUT. If these

pulses stop long enough for the voltage at LMP_C to decrease below 1.2 V, the lamp is reported off at bit

03 of the FLT/STAT register (0x02). . If LAMP_CTL transitions to high, requesting the inverter to turn on, and

LMP_C does not go above 1.2V before the FLT_DLY pin reaches 2.5V, an open lamp error signal is

produced and is stored, along with other error conditions, to bit zero of the FLT STATUS register 0x02. An

Open lamp fault will cause EN_OUT to go low. See FLT_DLY description. Zero to VDD input voltage range

FLT_DLY

Analog / Digital input to the open lamp comparator and latch. This input provides for a time out before

LMP_ON is sensed for an open lamp fault. The comparator has a 2.5V threshold. The comparator output is

latched when 2.5V is exceeded. The latch is reset at power on and when EN_OUT transitions to high. This

pin is normally connected to the C_TO pin of the LX1692 or 1693 CCFL controller.

EN_OUT

Digital Output. Enable output to CCFL controller. TTL voltage and current levels. EN_OUT is made high or

low by a write byte command to register 0x01. It is also reset by bit zero of register 0x02 going high.

PP

AA

CC

KK

AA

GG

EE

DD

AA

TT

AA

相关PDF资料 |

PDF描述 |

|---|---|

| LX1801CLQ-TR | SPECIALTY ANALOG CIRCUIT, PQCC16 |

| LY5150ALH | SPECIALTY ANALOG CIRCUIT, PBGA16 |

| LY5150ALHTR | SPECIALTY ANALOG CIRCUIT, PBGA16 |

| LZ34B1B | SPECIALTY ANALOG CIRCUIT, CQCC36 |

| M0336RA120 | 150 A, 1200 V, SILICON, RECTIFIER DIODE |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LX1801ILQ | 制造商:Microsemi Corporation 功能描述:ANALOG TO DIGITAL INTERFACE CONTROLLER - Bulk |

| LX1802 | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:PLUG for MED427A-1 |

| LX1810 | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ThermoElectric Cooler Drive Controller IC |

| LX1810CDB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Thermo Electric Controller IC |

| LX1810-CDB | 制造商:MICROSEMI 制造商全称:Microsemi Corporation 功能描述:ThermoElectric Cooler Drive Controller IC |

发布紧急采购,3分钟左右您将得到回复。