- 您现在的位置:买卖IC网 > PDF目录369885 > LXT334&LXT304A LXT334 & LXT304A - LXT334 & LXT304A ?Low Cost & High Performance Quad E1 Interface Solution PDF资料下载

参数资料

| 型号: | LXT334&LXT304A |

| 英文描述: | LXT334 & LXT304A - LXT334 & LXT304A ?Low Cost & High Performance Quad E1 Interface Solution |

| 中文描述: | LXT334 |

| 文件页数: | 11/32页 |

| 文件大小: | 395K |

| 代理商: | LXT334&LXT304A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

Dual T1/E1 Line Interface Unit

—

LXT331

Datasheet

11

a separate power supply pin (TVCC0 or TVCC1). Current limiters on the output drivers provide

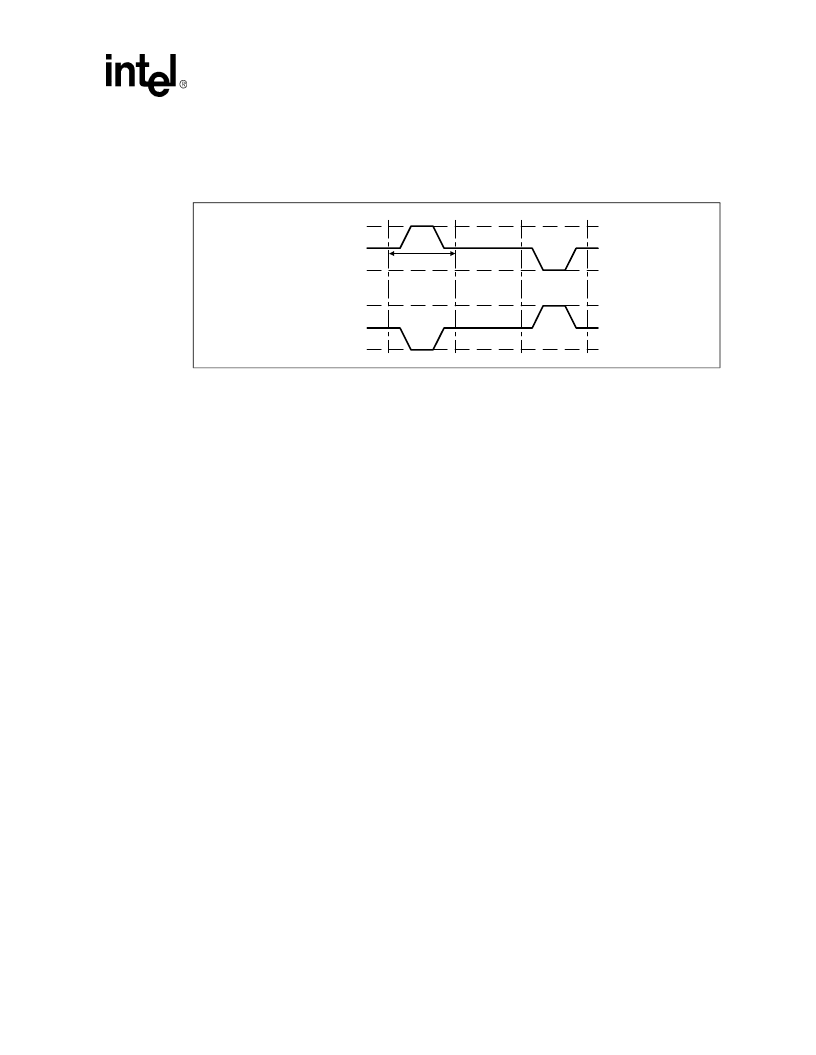

short circuit protection. Refer to Test Specifications for TCLK timing characteristics. As shown in

Figure 3

, the LXT331 encodes transmit data using 50% Alternate Mark Inversion (AMI) line code.

2.2.1

Pulse Shape

The transmitted pulse shape is determined by Line Length equalizer control signals LEN0 through

LEN2. Equalizer codes are hard-wired in Hardware mode as shown in

Table 2

. In Host mode, the

LEN

control codes are input through the serial interface. Shaped pulses are applied to the AMI line

driver for transmission onto the line at TTIP and TRING. The line driver provides a constant Low

output impedance of < 3

(typical) regardless of whether it is driving marks or spaces or during

transitions. This well-controlled impedance provides excellent return loss when used with external

precision resistors (±1% accuracy). See

Table 9

and

Table 10

for recommended transformer

specifications, turns ratios, series resistor (Rt) values, and typical return losses for various LEN

codes. To minimize power consumption the DC blocking capacitor and the LXT331 can be

connected directly to a 1:1.15 transformer without series resistors.

Pulses can be shaped for either 1.544 or 2.048 Mbps applications. 1.544 Mbps pulses for DSX-1

applications can be programmed to match line lengths from 0 to 655 feet of 22 AWG ABAM cable.

A combination of 9.1

resistors and a 1:2.3 transformer is recommended for maximum transmit

return loss in DSX-1 applications. The LXT331 also matches FCC pulse mask specifications for

CSU applications.

The LXT331 produces 2.048 Mbps pulses for both 75

coaxial (2.37 V) or 120

shielded

twisted-pair (3.0 V) lines through an output transformer with a 1:2 turns ratio.

Refer to the

“

Application Information

”

on page 20

for details on interface circuitry.

2.2.2

Driver Performance Monitor

The LXT331 incorporates a Driver Performance Monitor (DPM) as shown in

Figure 4 on page 13

.

The DPM output goes High on receipt of 63 consecutive zeros (at MTIP and MRING) and returns

Low on receipt of a transition. A reset command also drives the output signal Low.

The LXT331 uses its MTIP and MRING pins to monitor its own TTIP and TRING outputs or those

of an adjacent chip. Mark detection involves two criteria:

1. Voltage threshold: a pulse must trip a threshold voltage above or below (depending on its

polarity) the input bias voltage level. The LXT331 bias voltage is 2.5 V and the threshold for a

mark is 2.5 ± 0.79 V.

Figure 3. 50% AMI Coding

BIT CELL

TTIP

TRING

1

0

1

相关PDF资料 |

PDF描述 |

|---|---|

| LXT336QE | PCM RECEIVER|QUAD|CEPT PCM-30/E-1|CMOS|QFP|64PIN|PLASTIC |

| LXT350PE | PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|LDCC|28PIN|PLASTIC |

| LXT361LE | Telecommunication IC |

| LXT361PE | Telecommunication IC |

| LXT362LE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LXT335 | 制造商:LVL1 制造商全称:LVL1 功能描述:Quad Short Haul PCM Analog Interface |

| LXT336QE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM RECEIVER|QUAD|CEPT PCM-30/E-1|CMOS|QFP|64PIN|PLASTIC |

| LXT350 | 制造商:LVL1 制造商全称:LVL1 功能描述:Integrated T1/E1 S/H Transceivers With Crystal-less Jitter Attenuation |

| LXT350PE | 制造商:Intel 功能描述: |

| LXT350QE | 制造商:LEVEL1 功能描述: |

发布紧急采购,3分钟左右您将得到回复。