- 您现在的位置:买卖IC网 > PDF目录369885 > LXT362PE PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC PDF资料下载

参数资料

| 型号: | LXT362PE |

| 英文描述: | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC |

| 中文描述: | 的PCM收发器|单|的T 1(DS1的)|的CMOS | LDCC | 28脚|塑料 |

| 文件页数: | 20/52页 |

| 文件大小: | 1187K |

| 代理商: | LXT362PE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

LXT361

—

Integrated T1/E1 LH/SH Transceiver for DS1/DSX-1 or PRI Applications

20

Datasheet

With NLOOP detection enabled, the receiver looks for the NLOOP data patterns (00001 = enable,

001 = disable) in the input data stream. When the receiver detects an NLOOP enable data pattern

repeated for a minimum of five seconds, the device enables RLOOP. The device responds to both

framed and unframed NLOOP patterns. Once NLOOP detection is enabled at the chip and

activated by the appropriate data pattern, it is identical to Remote loopback (RLOOP). NLOOP is

disabled by receiving the 001 pattern for five seconds, or by activating RLOOP or ALOOP, or by

disabling NLOOP detection. The device goes into Dual loopback mode (DLOOP) in the case

where it detects both the NLOOP and LLOOP functions.

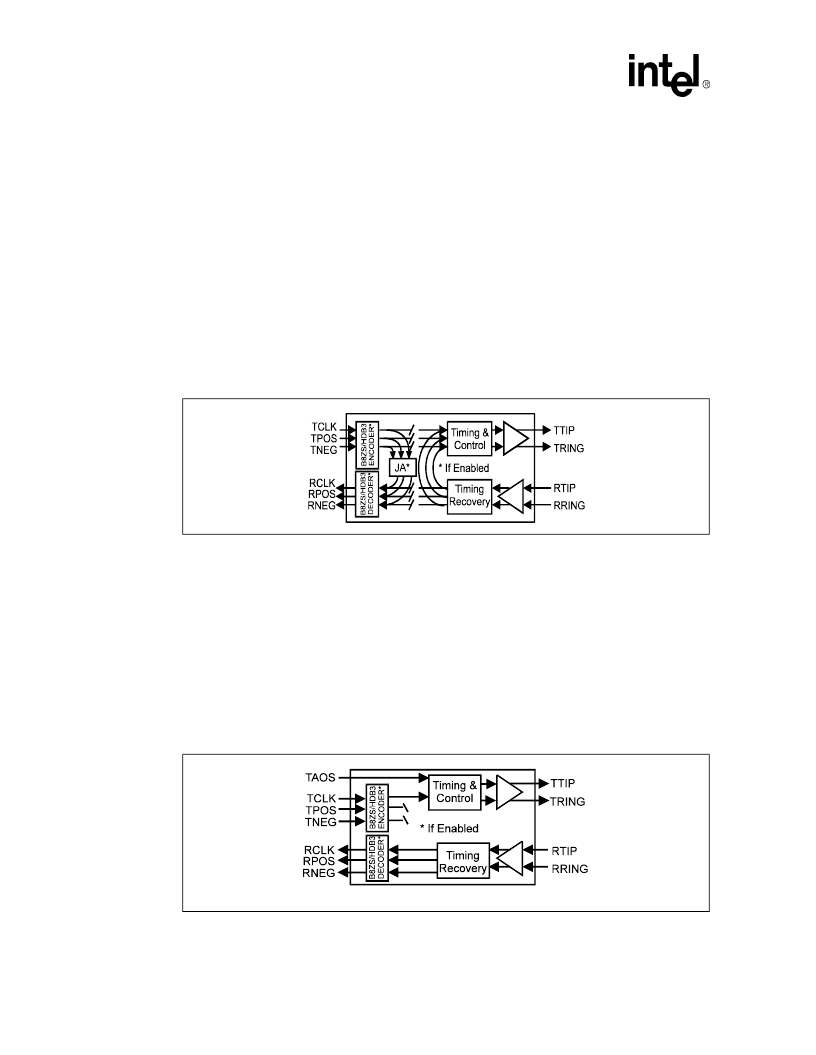

3.5.1.5

Dual Loopback

See

Figure 8

. To select Dual loopback (DLOOP) set bits CR2.ERLOOP and CR2.ELLOOP to 1. In

DLOOP mode, the transmit clock and data inputs (TCLK and TPOS/TNEG or TDATA) loop back

through the Jitter Attenuator (unless disabled) to RCLK and RPOS/RNEG or RDATA. The data

and clock recovered from the twisted-pair line loop back through the transmit circuits to TTIP and

TRING without jitter attenuation.

3.5.2

Internal Pattern Generation and Detection

3.5.2.1

Transmit All Ones

See

Figure 9

. In Transmit All Ones (TAOS) mode the transceiver ignores the TPOS and TNEG

inputs and transmits a continuous stream of 1s at the TCLK frequency. (With no TCLK, the TAOS

output clock is MCLK.) This can be used as the Alarm Indication Signal (AIS

–

also called the Blue

Alarm). TAOS is commanded by writing a 1 to bit CR2.ETAOS. Both TAOS and Local loopback

can occur simultaneously as shown in

Figure 4

, however, Remote loopback inhibits TAOS. When

both TAOS and LLOOP are active, TCLK and TPOS/TNEG loop back to RCLK and RPOS/RNEG

through the jitter attenuator (if enabled), and an all ones pattern goes to TTIP/TRING.

Figure 8. Dual Loopback

Figure 9. TAOS Data Path

相关PDF资料 |

PDF描述 |

|---|---|

| LXT362QE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363LE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363PE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC |

| LXT363QE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT360LE | PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|QFP|44PIN|PLASTIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LXT362QE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363LE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363PE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC |

| LXT363QE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT36X/35X | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LXT36x/35x - LXT36x/35x Master Clock Requirements |

发布紧急采购,3分钟左右您将得到回复。