- 您现在的位置:买卖IC网 > PDF目录369885 > LXT362PE PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC PDF资料下载

参数资料

| 型号: | LXT362PE |

| 英文描述: | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC |

| 中文描述: | 的PCM收发器|单|的T 1(DS1的)|的CMOS | LDCC | 28脚|塑料 |

| 文件页数: | 29/52页 |

| 文件大小: | 1187K |

| 代理商: | LXT362PE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

Integrated T1/E1 LH/SH Transceiver for DS1/DSX-1 or PRI Applications

—

LXT361

Datasheet

29

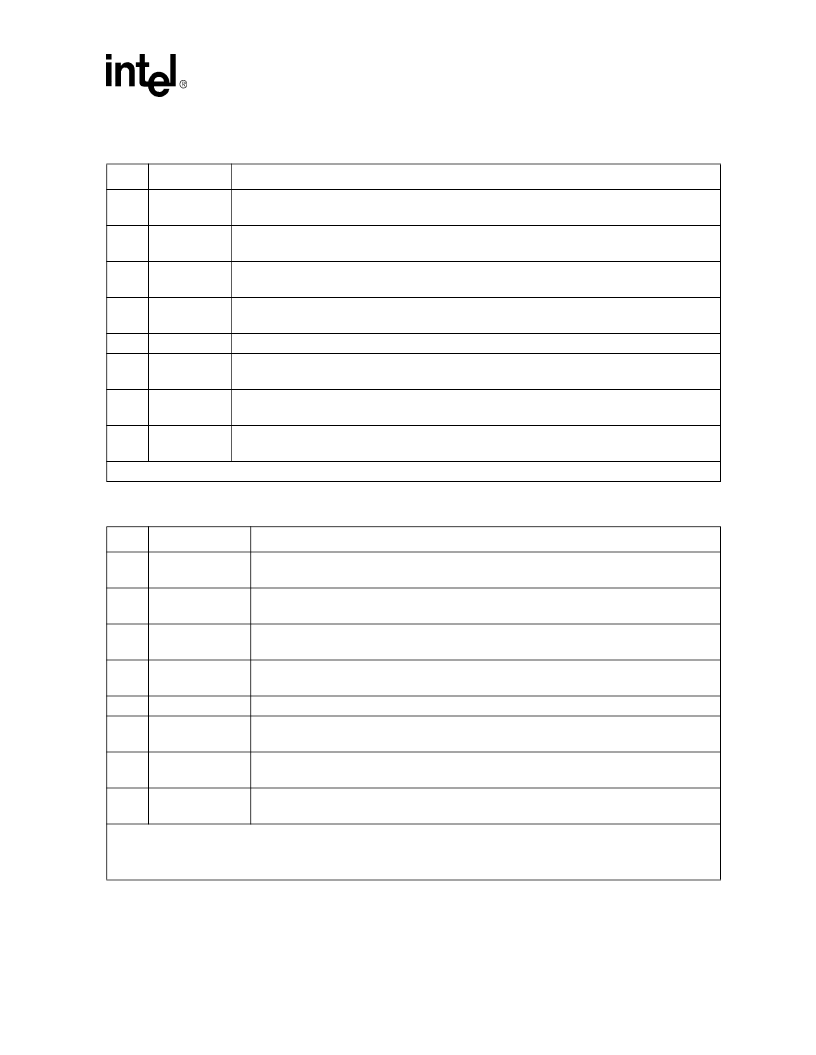

Table 11. Interrupt Clear Register

Read/Write, Address (A7-A0) = x010011x

Bit

Name

Function

1

0

CLOS

1 = Clear/Mask Loss of Signal interrupt.

0 = Enable Loss of Signal interrupt.

1

CNLOOP

1 = Clear/Mask Network loopback interrupt.

0 = Enable Network loopback interrupt.

2

CAIS

1 = Clear/Mask Alarm Indication Signal interrupt.

0 = Enable Alarm Indication Signal interrupt.

3

CQRSS

1 = Clear/Mask Quasi-Random Signal Source interrupt.

0 = Enable Quasi-Random Signal Source interrupt.

4

-

reserved

–

set to 1 for normal operation.

5

CDFMO

1 = Clear/Mask Driver Failure Monitor Open interrupt.

0 = Enable Driver Failure Monitor Open interrupt.

6

CESO

1 = Clear/Mask Elastic Store Overflow interrupt.

0 = Enable Elastic Store Overflow interrupt.

7

CESU

1 = Clear/Mask Elastic Store Underflow interrupt.

0 = Enable Elastic Store Underflow interrupt.

1. Leaving a 1 of in any of these bits masks the associated interrupt.

Table 12. Transition Status Register

Read Only, Address (A7-A0) = x010100x

Bit

Name

Function

0

TLOS

1 = Loss of Signal (LOS) has changed since last clear LOS interrupt occurred.

0 = No change in status.

1

TNLOOP

1 = NLOOP has changed since last clear NLOOP interrupt occurred.

0 = No change in status.

2

TAIS

1 = AIS has changed since last clear AIS interrupt occurred.

0 = No change in status.

3

TQRSS

1 = QRSS has changed since last clear QRSS interrupt occurred

1

.

0 = No change in status.

4

-

reserved-ignore.

5

TDFMO

1 = DFMO has changed since last clear DFMS interrupt occurred.

0 = No change in status.

6

ESOVR

1 = ES overflow status sticky bit

2

.

0 = No change in status.

7

ESUNF

1 = ES underflow status sticky bit

2

.

0 = No change in status.

1. A QRSS transition indicates receive QRSS pattern sync or loss. A simple error in QRSS pattern is not reported as a

transition.

2. Tripping the overflow or underflow indicator in the ES sets the ESOVR/ESUNF status bit(s). Reading the Transition Status

Register clears these bits. Setting CESO and CESU in the Interrupt Clear Register masks these interrupts.

相关PDF资料 |

PDF描述 |

|---|---|

| LXT362QE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363LE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363PE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC |

| LXT363QE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT360LE | PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|QFP|44PIN|PLASTIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LXT362QE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363LE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363PE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC |

| LXT363QE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT36X/35X | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LXT36x/35x - LXT36x/35x Master Clock Requirements |

发布紧急采购,3分钟左右您将得到回复。