- 您现在的位置:买卖IC网 > PDF目录224123 > M25P32VMN6G (意法半导体) 4 Mbit Uniform Sector, Serial Flash Memory PDF资料下载

参数资料

| 型号: | M25P32VMN6G |

| 厂商: | 意法半导体 |

| 元件分类: | FLASH |

| 英文描述: | 4 Mbit Uniform Sector, Serial Flash Memory |

| 中文描述: | 4兆位统一部门,串行闪存 |

| 文件页数: | 14/39页 |

| 文件大小: | 506K |

| 代理商: | M25P32VMN6G |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页

21/39

M25P32

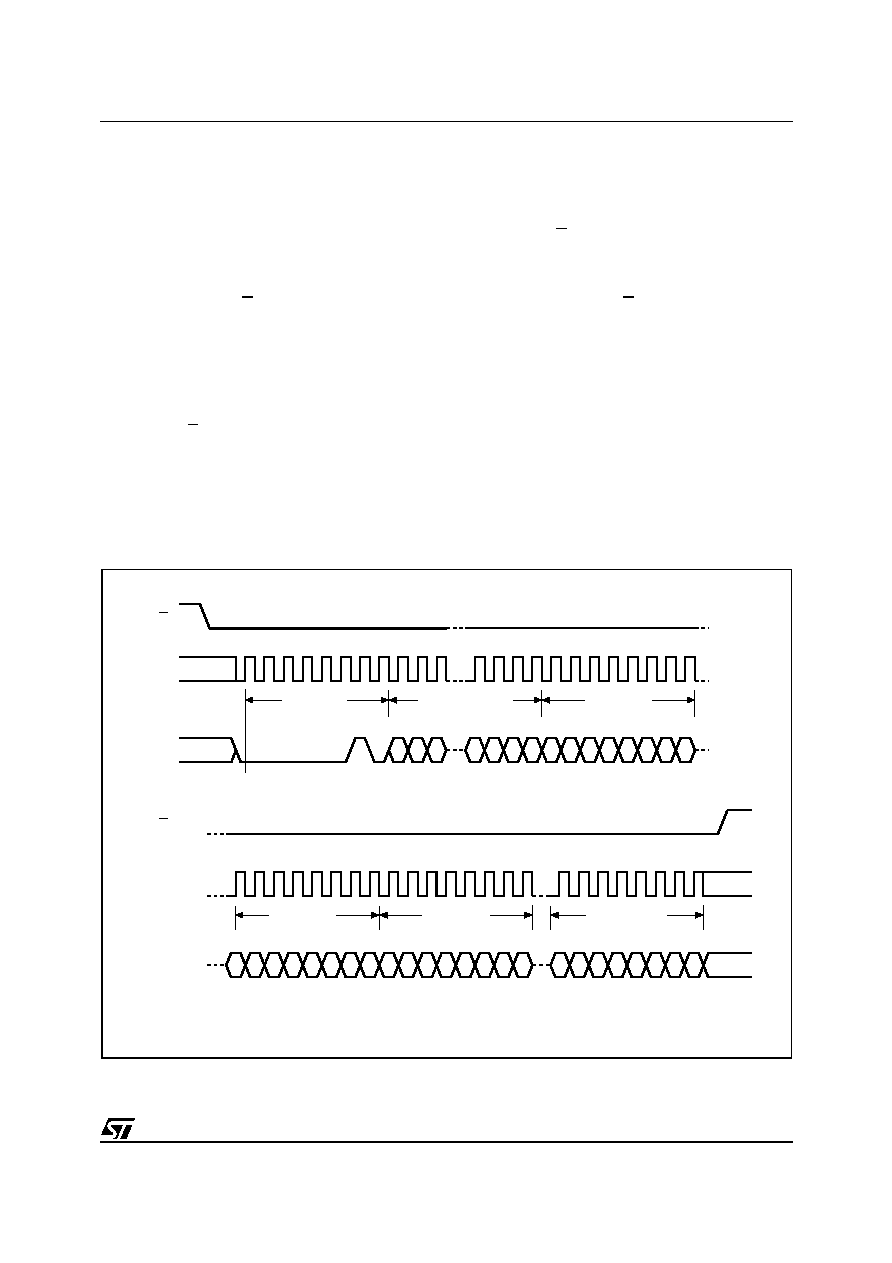

Page Program (PP)

The Page Program (PP) instruction allows bytes to

be programmed in the memory (changing bits from

1 to 0). Before it can be accepted, a Write Enable

(WREN) instruction must previously have been ex-

ecuted. After the Write Enable (WREN) instruction

has been decoded, the device sets the Write En-

able Latch (WEL).

The Page Program (PP) instruction is entered by

driving Chip Select (S) Low, followed by the in-

struction code, three address bytes and at least

one data byte on Serial Data Input (D). If the 8

least significant address bits (A7-A0) are not all

zero, all transmitted data that goes beyond the end

of the current page are programmed from the start

address of the same page (from the address

whose 8 least significant bits (A7-A0) are all zero).

Chip Select (S) must be driven Low for the entire

duration of the sequence.

The instruction sequence is shown in Figure 16..

If more than 256 bytes are sent to the device, pre-

viously latched data are discarded and the last 256

data bytes are guaranteed to be programmed cor-

rectly within the same page. If less than 256 Data

bytes are sent to device, they are correctly pro-

grammed at the requested addresses without hav-

ing any effects on the other bytes of the same

page.

Chip Select (S) must be driven High after the

eighth bit of the last data byte has been latched in,

otherwise the Page Program (PP) instruction is not

executed.

As soon as Chip Select (S) is driven High, the self-

timed Page Program cycle (whose duration is tPP)

is initiated. While the Page Program cycle is in

progress, the Status Register may be read to

check the value of the Write In Progress (WIP) bit.

The Write In Progress (WIP) bit is 1 during the self-

timed Page Program cycle, and is 0 when it is

completed. At some unspecified time before the

cycle is completed, the Write Enable Latch (WEL)

bit is reset.

A Page Program (PP) instruction applied to a page

which is protected by the Block Protect (BP2, BP1,

ed.

Figure 16. Page Program (PP) Instruction Sequence

Note: Address bits A23 to A22 are Don’t Care.

C

D

AI04082B

S

42

41

43 44 45 46 47 48 49 50

52 53 54 55

40

C

D

S

23

2

1

3456789 10

28 29 30 31 32 33 34 35

22 21

3210

36 37 38

Instruction

24-Bit Address

0

765432

0

1

Data Byte 1

39

51

765432

0

1

Data Byte 2

765432

0

1

Data Byte 3

Data Byte 256

2079

2078

2077

2076

2075

2074

2073

765432

0

1

2072

MSB

相关PDF资料 |

PDF描述 |

|---|---|

| M25P32VMN6P | 4 Mbit Uniform Sector, Serial Flash Memory |

| M25P32VMN6T | 4 Mbit Uniform Sector, Serial Flash Memory |

| M25P32VMN6TG | 4 Mbit Uniform Sector, Serial Flash Memory |

| M25P32VMN6TP | 4 Mbit Uniform Sector, Serial Flash Memory |

| M25P32VMP3 | 4 Mbit Uniform Sector, Serial Flash Memory |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M25P32VMN6P | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:512 Kbit to 32 Mbit, Low Voltage, Serial Flash Memory With 40 MHz or 50 MHz SPI Bus Interface |

| M25P32VMN6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:512 Kbit to 32 Mbit, Low Voltage, Serial Flash Memory With 40 MHz or 50 MHz SPI Bus Interface |

| M25P32VMN6TG | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:512 Kbit to 32 Mbit, Low Voltage, Serial Flash Memory With 40 MHz or 50 MHz SPI Bus Interface |

| M25P32VMN6TP | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:512 Kbit to 32 Mbit, Low Voltage, Serial Flash Memory With 40 MHz or 50 MHz SPI Bus Interface |

| M25P32VMP3 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:512 Kbit to 32 Mbit, Low Voltage, Serial Flash Memory With 40 MHz or 50 MHz SPI Bus Interface |

发布紧急采购,3分钟左右您将得到回复。