- 您现在的位置:买卖IC网 > PDF目录45029 > M37161MF-XXXSP 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 PDF资料下载

参数资料

| 型号: | M37161MF-XXXSP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| 封装: | 0.600 INCH, 1.78 MM PITCH, PLASTIC, SDIP-42 |

| 文件页数: | 56/129页 |

| 文件大小: | 1092K |

| 代理商: | M37161MF-XXXSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页

Rev.1.00

2003.11.25

page 32 of 128

M37161M8/MA/MF-XXXSP/FP,M37161EFSP/FP

8.6.3 I2C Clock Control Register

The I2C clock control register (address 00FA16) is used to set ACK

control, SCL mode and SCL frequency.

(1) Bits 0 to 4: SCL frequency control bits (CCR0–CCR4)

These bits control the SCL frequency.

(2) Bit 5: SCL mode specification bit (FAST MODE)

This bit specifies the SCL mode. When this bit is set to “0,” the stan-

dard clock mode is set. When the bit is set to “1,” the high-speed

clock mode is set.

(3) Bit 6: ACK bit (ACK BIT)

This bit sets the SDA status when an ACK clock is generated. When

this bit is set to “0,” the ACK return mode is set and SDA goes to

LOW at the occurrence of an ACK clock. When the bit is set to “1,”

the ACK non-return mode is set. The SDA is held in the HIGH status

at the occurrence of an ACK clock.

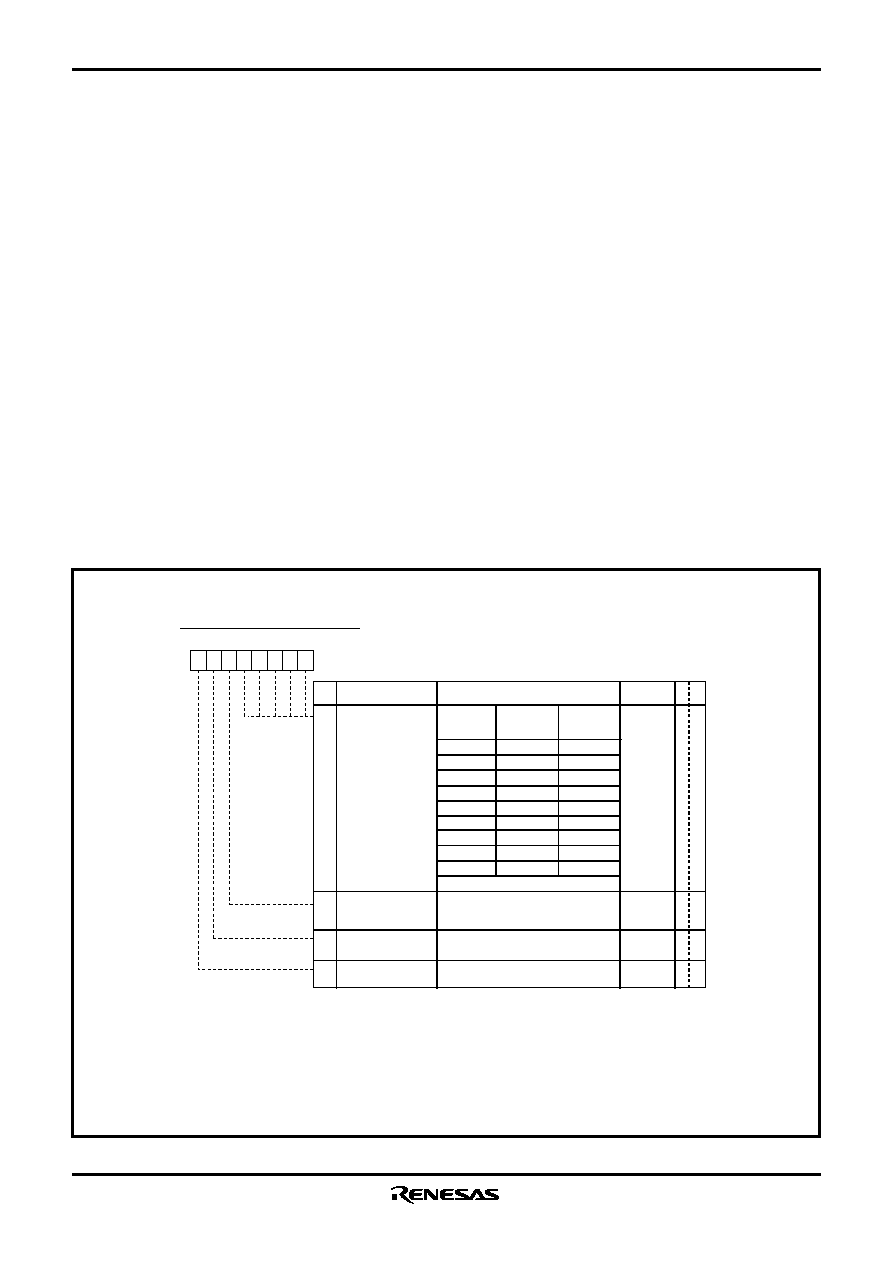

Fig. 8.6.4 I2C Clock Control Register

However, when the slave address matches the address data in the

reception of address data at ACK BIT = “0,” the SDA is automatically

goes to LOW (ACK is returned). If there is a mismatch between the

slave address and the address data, the SDA is automatically goes

to HIGH (ACK is not returned).

ACK clock: Clock for acknowledgement

(4) Bit 7: ACK clock bit (ACK)

This bit specifies a mode of acknowledgment which is an acknowl-

edgment response of data transmission. When this bit is set to “0,”

the no ACK clock mode is set. In this case, no ACK clock occurs

after data transmission. When the bit is set to “1,” the ACK clock

mode is set and the master generates an ACK clock upon comple-

tion of each 1-byte data transmission.The device for transmitting

address data and control data releases the SDA at the occurrence of

an ACK clock (make SDA HIGH) and receives the ACK bit generated

by the data receiving device.

Note: Do not write data into the I2C clock control register during transmission.

If data is written during transmission, the I2C clock generator is reset, so

that data cannot be transmitted normally.

b7 b6 b5 b4 b3 b2 b1 b0

I2C clock control register (S2) [Address 00FA16]

I2C Clock Control Register

0

to

4

SCL frequency control

bits

(CCR0 to CCR4)

7

5

6

SCL mode

specification bit

(FAST MODE)

0: Standard clock mode

1: High-speed clock mode

0

Standard

clock

mode

Functions

Name

After reset

RW

B

0

ACK bit

(ACK BIT)

ACK clock bit

(ACK)

0: ACK is returned.

1: ACK is not returned.

0: No ACK clock

1: ACK clock

High speed

clock mode

Setup disabled

00 to 02

Setup disabled

333

03

Setup disabled

250

04

100

400 (See note)

05

83.3

166

06

500/CCR value 1000/CCR value

...

17.2

34.5

1D

16.6

33.3

1E

16.1

32.3

1F

(

φ = at 4 MHz, unit : kHz)

Notes 1. At 400kHz in the high-speed clock mode, the duty is as below .

“0” period : “1” period = 3 : 2

In the other cases, the duty is as below.

“0” period : “1” period = 1 : 1

Setup value

of CCR4–

CCR0

RW

相关PDF资料 |

PDF描述 |

|---|---|

| M37161EFSP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| M37161MA-XXXSP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| M37161M8-XXXSP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| M37202E3SP | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PDIP64 |

| M37207EFFP | 8-BIT, OTPROM, 8.1 MHz, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M3720 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:1 KEY 1 SOUND |

| M3720-1 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:1 KEY 1 SOUND |

| M3720-10 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:1 KEY 1 SOUND |

| M3720-2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:1 KEY 1 SOUND |

| M3720-3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:1 KEY 1 SOUND |

发布紧急采购,3分钟左右您将得到回复。