- 您现在的位置:买卖IC网 > PDF目录180214 > M4LV-96/48-12VI (LATTICE SEMICONDUCTOR CORP) High Performance E 2 CMOS In-System Programmable Logic PDF资料下载

参数资料

| 型号: | M4LV-96/48-12VI |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | High Performance E 2 CMOS In-System Programmable Logic |

| 中文描述: | EE PLD, 12 ns, PQFP100 |

| 封装: | TQFP-100 |

| 文件页数: | 9/46页 |

| 文件大小: | 754K |

| 代理商: | M4LV-96/48-12VI |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

MACH 4 Family

17

PAL Block Clock Generation

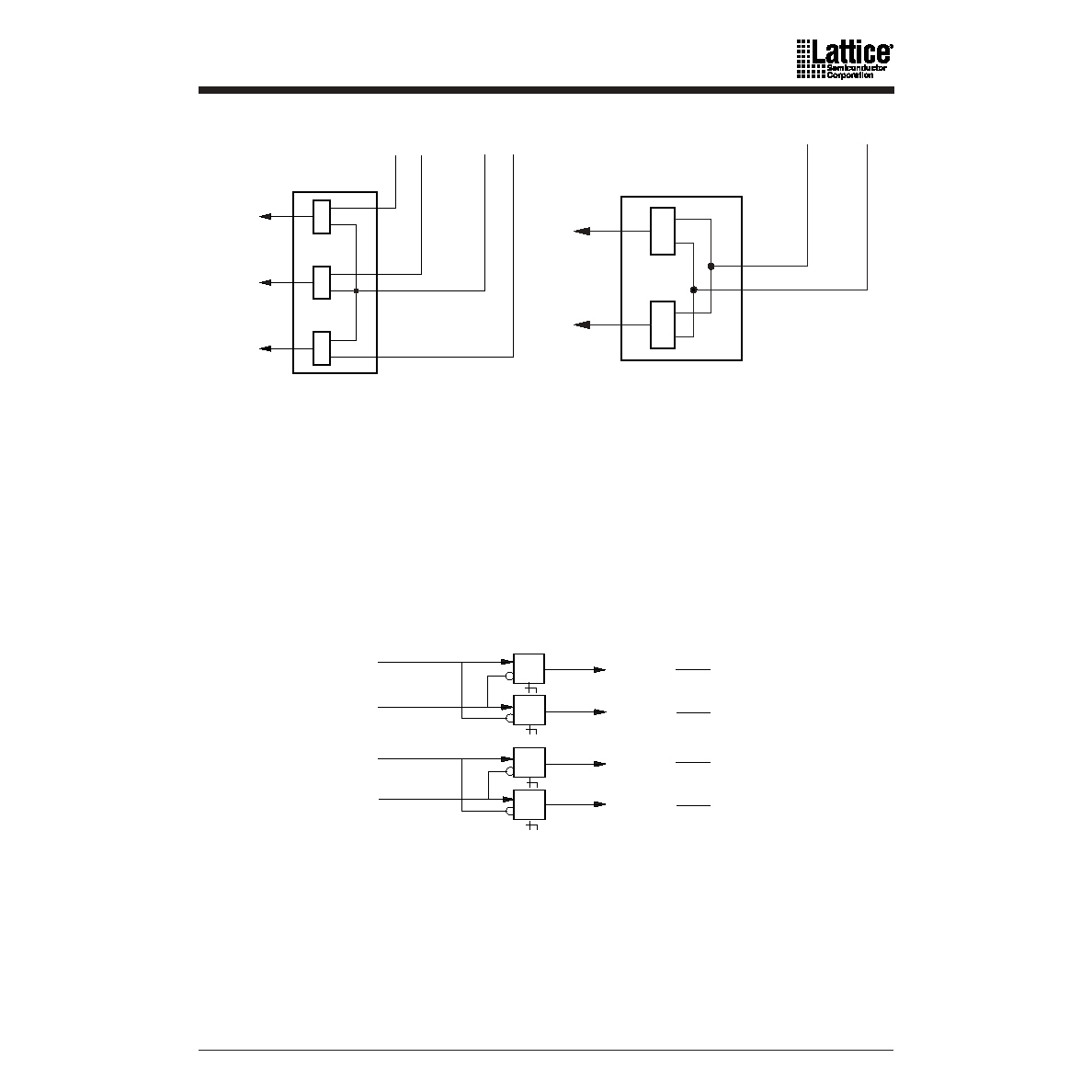

Each MACH 4 device has four clock pins that can also be used as inputs. These pins drive a

clock generator in each PAL block (Figure 14). The clock generator provides four clock signals

that can be used anywhere in the PAL block. These four PAL block clock signals can consist of

a large number of combinations of the true and complement edges of the global clock signals.

Table 12 lists the possible combinations.

Note:

1. M4(LV)-32/32 and M4(LV)-64/32 have only two clock pins, GCLK0 and GCLK1. GCLK2 is tied to GCLK0, and GCLK3 is tied to

GCLK1.

To

Central

Switch

Matrix

From

Macrocell

2

From Input Cell

Direct

From

Macrocell

1

Registered/Latched

17466G-002

17466G-003

Figure 12. MACH 4 with 2:1 Macrocell-I/O Cell Ratio

- Input Switch Matrix

Figure 13. MACH 4 with 1:1 Macrocell-I/O Cell Ratio

- Input Switch Matrix

To

Central

Switch

Matrix

From

Macrocell

From

I/O

Pin

GCLK0

GCLK1

GCLK2

GCLK3

Block CLK0

(GCLK0 or GCLK1)

Block CLK1

(GCLK1 or GCLK0)

Block CLK2

(GCLK2 or GCLK3)

Block CLK3

(GCLK3 or GCLK2)

17466G-004

Figure 14. PAL Block Clock Generator 1

相关PDF资料 |

PDF描述 |

|---|---|

| M4LV-96/48-15VC | High Performance E 2 CMOS In-System Programmable Logic |

| M4LV-96/48-18VI | High Performance E 2 CMOS In-System Programmable Logic |

| M4LV-96/48-7VC | High Performance E 2 CMOS In-System Programmable Logic |

| M4LV-256/128-10YI | High Performance E 2 CMOS In-System Programmable Logic |

| M4LV-64/32-18VI | High Performance E 2 CMOS In-System Programmable Logic |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M4M | 功能描述:XLR 连接器 4P ADAPT RECEPTACLE RoHS:否 制造商:Neutrik 标准:Standard XLR 产品类型:Connectors 型式:Female 位置/触点数量:3 端接类型:Solder 安装风格:Cable 方向:Vertical |

| M4-M | 制造商:Tamura Corporation of America 功能描述: |

| M4M/S SS PS | 制造商:NUTS 功能描述: |

| M4M/S ST ZC | 制造商:NUTS 功能描述: |

| M4M1 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MEDIUM CURRENT SILICON RECTIFIERS |

发布紧急采购,3分钟左右您将得到回复。