- 您现在的位置:买卖IC网 > PDF目录180224 > M5-384/160-15YC (LATTICE SEMICONDUCTOR CORP) Fifth Generation MACH Architecture PDF资料下载

参数资料

| 型号: | M5-384/160-15YC |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | Fifth Generation MACH Architecture |

| 中文描述: | EE PLD, 15 ns, PQFP208 |

| 封装: | PLASTIC, QFP-208 |

| 文件页数: | 39/42页 |

| 文件大小: | 938K |

| 代理商: | M5-384/160-15YC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页

6MACH 5 Family

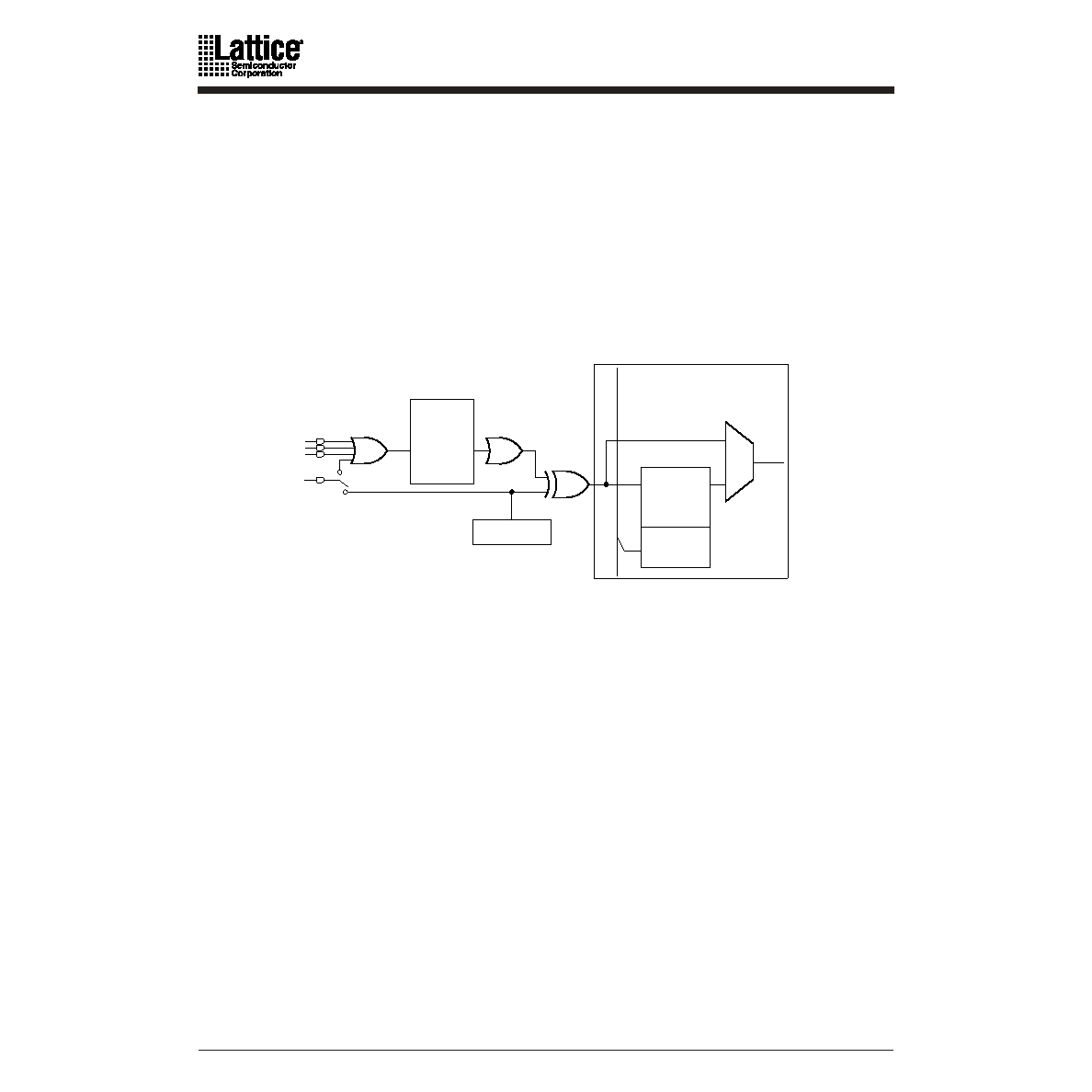

Macrocells

The macrocells for MACH 5 devices consist of a storage element which can be congured for

combinatorial, registered or latched operation (Figure 3). The D-type ip-ops can be congured

as T-type, J-K, or S-R operation through the use of the XOR gate associated with each macrocell.

Each PAL block has the capability to provide two input registers by using macrocells 0 and 15. In

order to use this option, these macrocells must be accessed via the I/O pins associated with

macrocells 3 and 12, respectively. Once the macrocell is used as an input register, it cannot be used

for logic, so its clusters can be re-directed through the logic allocator to another macrocell. The

I/O pins associated with macrocells 0 and 15 can still be used as input pins. Although the I/O pins

for macrocells 3 and 12 are used to connect to the input registers, these macrocells can still be

used as “buried” macrocells to drive device logic via the matrix.

Control Generator

The control generator provides four congurable clock lines and three congurable set/reset lines to

each macrocell in a PAL block. Any of the four clock lines and any of the three set/reset lines can

be independently selected by any ip-op within a block. The clock lines can be congured to

provide synchronous global (pin) clocks and asynchronous product term clocks, sum term clocks,

and latch enables (Figure 4). Three of the four global clocks, as well as two product-term clocks

and one sum-term clock, are available per PAL block. Positive or negative edge clocking is

available as well as advanced clocking features such as

complementary and biphase clocking.

Complementary clocking provides two clock lines exactly 180 degrees out of phase, and is useful

in applications such as fast data paths. A biphase clock line clocks ip-ops on both the positive

and negative edges of the clock. The conguration options for the four clock lines per PAL block

are as follows:

Clock Line 0 Options

◆

Global clock (0, 1, 2, or 3) with positive or negative edge clock enable

◆

Product-term clock (A*B*C)

◆

Sum-term clock (A+B+C)

Logic

Allocator

5-8

Clusters/

MC

Prog. Polarity

Mode

Selection

Control

Bus

Macrocell

D

Q

20446G-003

Figure 3. Macrocell Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| M5-384/160-15YI | Fifth Generation MACH Architecture |

| M5-384/160-20YI | Fifth Generation MACH Architecture |

| M5-384/160-6YC | Fifth Generation MACH Architecture |

| M5-384/160-7YC | Fifth Generation MACH Architecture |

| M5-384/160-7YI | Fifth Generation MACH Architecture |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M5386 | 制造商:Tamura Corporation of America 功能描述: |

| M-538CT | 制造商:NEC 制造商全称:NEC 功能描述:DC Line Fileters |

| M539 | 制造商:MA-COM 制造商全称:M/A-COM Technology Solutions, Inc. 功能描述:Drivers for GaAs FET MMIC Switches and Digital Attenuators |

| M5390 NC001 | 制造商:Alpha Wire Company 功能描述:CBL 2COND 18AWG NC 1000' |

| M5390 NC002 | 制造商:Alpha Wire Company 功能描述:CBL 2COND 18AWG NC 500' |

发布紧急采购,3分钟左右您将得到回复。