- 您现在的位置:买卖IC网 > PDF目录45052 > M8803F3Y-90T1T (STMICROELECTRONICS) 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 PDF资料下载

参数资料

| 型号: | M8803F3Y-90T1T |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

| 封装: | PLASTIC, QFP-52 |

| 文件页数: | 18/85页 |

| 文件大小: | 601K |

| 代理商: | M8803F3Y-90T1T |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页

25/85

M88 FAMILY

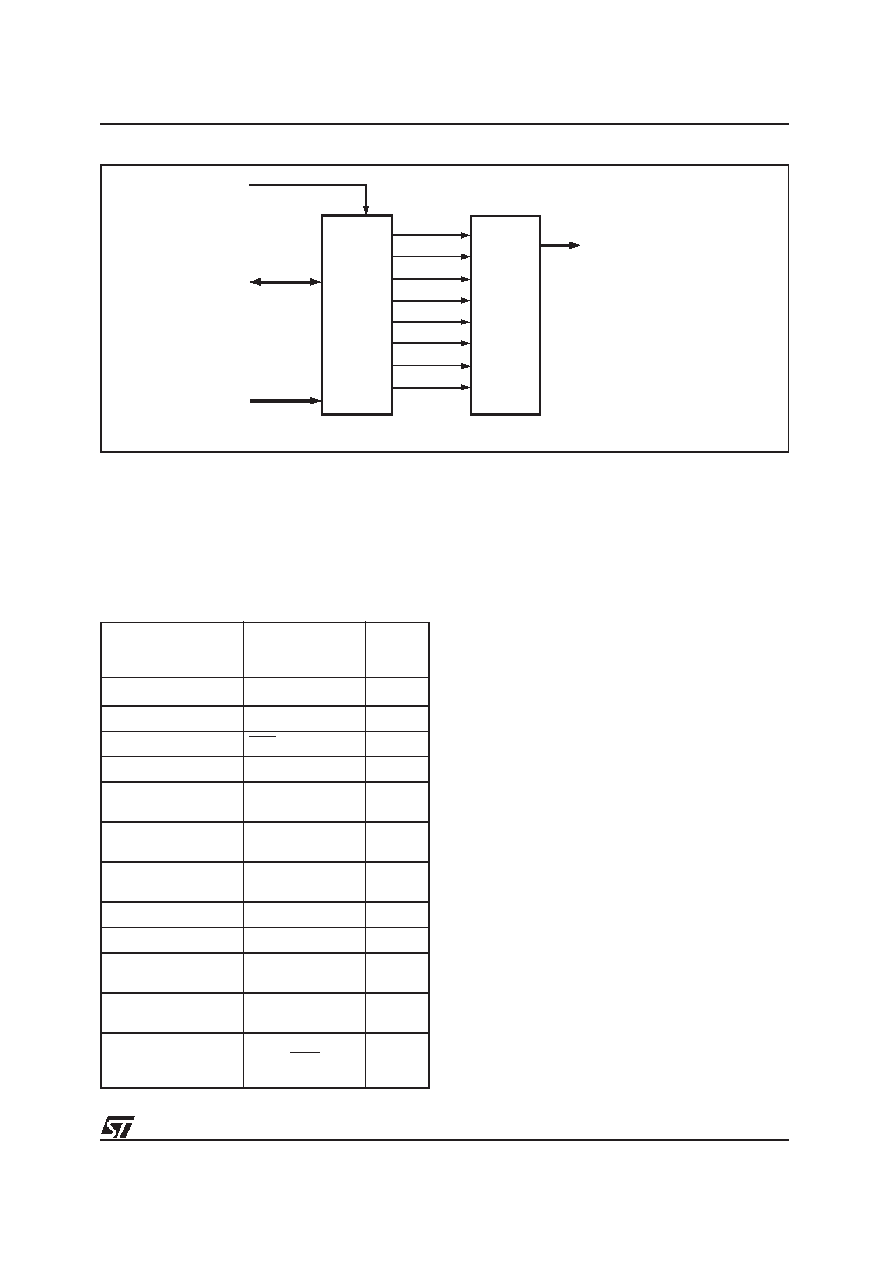

Figu re 13. Page Register

RESET

D0 - D7

R/ W

D0

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

D1

D2

D3

D4

D5

D6

D7

PAGE

REGISTER

PGR0

PGR1

PGR2

PGR3

FLASH

DPLD

AND

FLASH

CPLD

INTERNAL

SELECTS

AND LOGIC

FLASH

PLD

PGR4

PGR5

PGR6

PGR7

AI02871

Decode PLD (DPLD)

The DPLD, shown in Figure 15, is used for

decoding the address for internal and external

components.

The

DPLD

can

generate

the

following decode signals:

s

8 sector selects for the main Flash memory

(three product terms each)

s

4 sector selects for the optional EEPROM or

Flash Boot memory (three product terms each)

s

1 internal SRAM select signal (two product

terms)

s

1 internal CSIOP (PSD configuration register)

select signal

s

1 JTAG select signal (enables JTAG on Port C)

s

2 internal peripheral select signals

(peripheral I/O mode).

Complex PLD (CPLD)

The CPLD can be used to implement system logic

functions, such as loadable counters and shift

registers,

syst em

mailboxes,

handshaking

protocols, state machines, and random logic. The

CPLD can also be used to generate 3 external

chip selects, routed to Port D.

Although external chip selects can be produced by

any Output Macrocell, these three external chip

selects on Port D do not consume any Output

Macrocells.

As shown in Figure 14, the CPLD has the following

blocks:

s

24 Input Macrocells (IMCs)

s

16 Output Macrocells (OMCs)

s

Macrocell Allocator

s

Product Term Allocator

s

AND array capable of generating up to 140

product terms

s

Four I/O ports.

Table 17. DPLD and CPLD Inpu ts

Note: 1. The address inputs are A[19:4] in 80C51XA mode.

Input Source

Input Name

Number

of

Sign als

MCU Address Bus1

A[15:0]

16

MCU Control Signals

CNTL[2:0]

3

Reset

RST

1

Power Down

PDN

1

Port A Input

Macrocells

PA[7-0]

8

Port B Input

Macrocells

PB[7-0]

8

Port C Input

Macrocells

PC[7-0]

8

Port D Inputs

PD[2:0]

3

Page Register

PGR(7:0)

8

Macrocell AB

Feedback

MCELLAB.FB[7:0]

8

Macrocell BC

Feedback

MCELLBC.FB[7:0]

8

EEPROM/Boot Flash

Programming Status

Bit

Ready/Busy

1

相关PDF资料 |

PDF描述 |

|---|---|

| M8803F2W-15T1T | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

| M8813F2W-15K1 | 128K X 8 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQCC52 |

| M8813F3W-15T1 | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

| M8803F2Y-90T1 | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

| M8803F3Y-90T1 | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M8805/100-007 | 制造商:OTTO Engineering Inc 功能描述:M8805/100-007 |

| M8805/100-009 | 制造商:OTTO Engineering Inc 功能描述:M8805/100-009 |

| M8805/100-010 | 制造商:OTTO Engineering Inc 功能描述:M8805/100-010 |

| M8805/100-015 | 制造商:OTTO Engineering Inc 功能描述:M8805/100-015 |

| M8805/100-016 | 制造商:OTTO Engineering Inc 功能描述:M8805/100-016 |

发布紧急采购,3分钟左右您将得到回复。