- 您现在的位置:买卖IC网 > PDF目录262949 > M95010-WDW3TR (STMICROELECTRONICS) 128 X 8 SPI BUS SERIAL EEPROM, PDSO8 PDF资料下载

参数资料

| 型号: | M95010-WDW3TR |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | PROM |

| 英文描述: | 128 X 8 SPI BUS SERIAL EEPROM, PDSO8 |

| 封装: | 0.169 INCH, TSSOP-8 |

| 文件页数: | 37/37页 |

| 文件大小: | 586K |

| 代理商: | M95010-WDW3TR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页

9/37

M95040, M95020, M95010

OPERATING FEATURES

Power-up

When the power supply is turned on, VCC rises

from VSS to VCC.

During this time, the Chip Select (S) must be al-

lowed to follow the VCC voltage. It must not be al-

lowed to float, but should be connected to VCC via

a suitable pull-up resistor.

As a built in safety feature, Chip Select (S) is edge

sensitive as well as level sensitive. After Power-

up, the device does not become selected until a

falling edge has first been detected on Chip Select

(S). This ensures that Chip Select (S) must have

been High, prior to going Low to start the first op-

eration.

Power-down

At Power-down, the device must be deselected.

Chip Select (S) should be allowed to follow the

voltage applied on VCC.

Active Power and Standby Power Modes

When Chip Select (S) is Low, the device is select-

ed, and in the Active Power mode. The device

When Chip Select (S) is High, the device is dese-

lected. If an Erase/Write cycle is not currently in

progress, the device then goes in to the Standby

Power mode, and the device consumption drops

to ICC1.

Hold Condition

The Hold (HOLD) signal is used to pause any se-

rial communications with the device without reset-

ting the clocking sequence.

During the Hold condition, the Serial Data Output

(Q) is high impedance, and Serial Data Input (D)

and Serial Clock (C) are Don’t Care.

To enter the Hold condition, the device must be

selected, with Chip Select (S) Low.

Normally, the device is kept selected, for the whole

duration of the Hold condition. Deselecting the de-

vice while it is in the Hold condition, has the effect

of resetting the state of the device, and this mech-

anism can be used if it is required to reset any pro-

cesses that had been in progress.

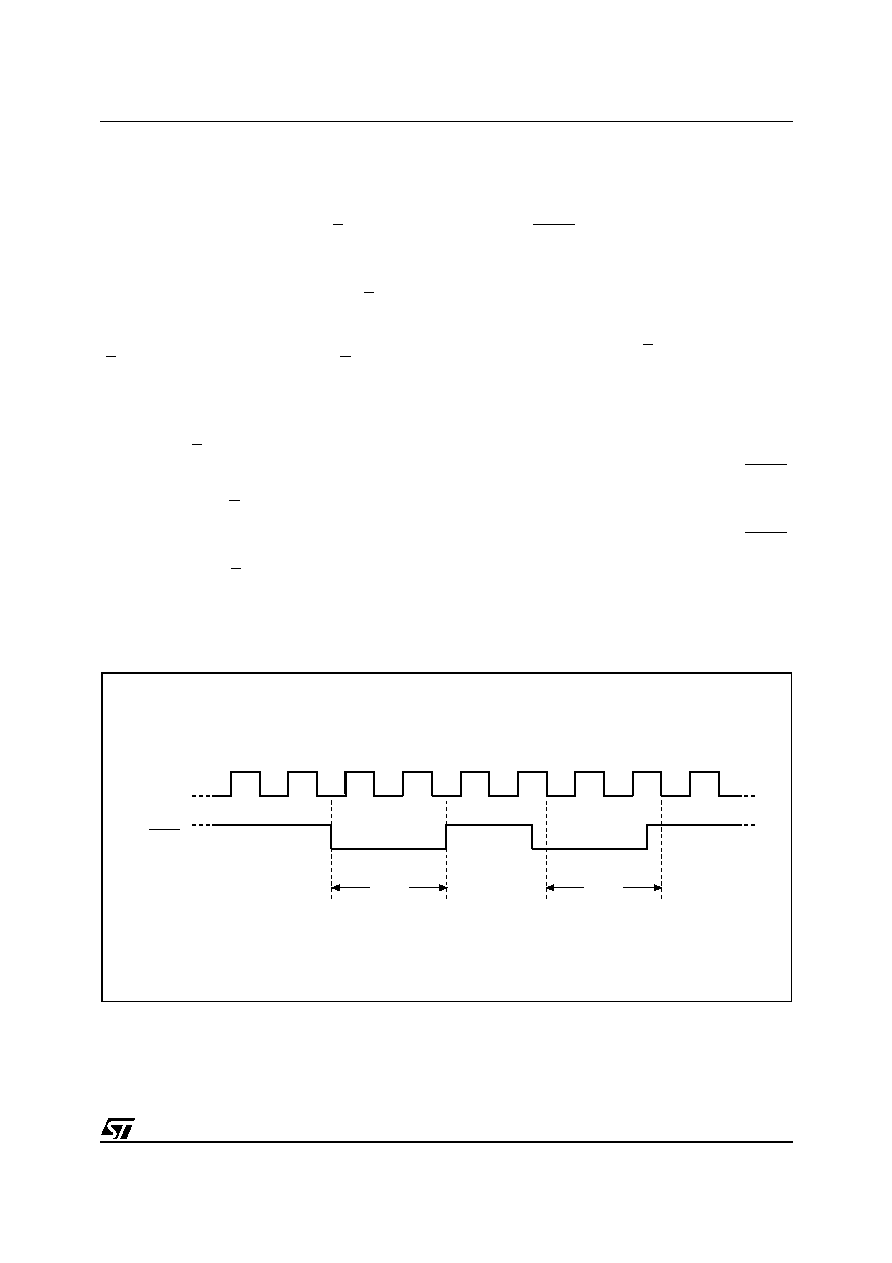

The Hold condition starts when the Hold (HOLD)

signal is driven Low at the same time as Serial

Clock (C) already being Low (as shown in Figure

The Hold condition ends when the Hold (HOLD)

signal is driven High at the same time as Serial

Clock (C) already being Low.

Figure 6. also shows what happens if the rising

and falling edges are not timed to coincide with

Serial Clock (C) being Low.

Figure 6. Hold Condition Activation

AI02029D

HOLD

C

Hold

Condition

Hold

Condition

相关PDF资料 |

PDF描述 |

|---|---|

| MT46V32M4FJ-6 | 32M X 4 DDR DRAM, 0.7 ns, PBGA60 |

| MT46H16M32LFB5-6IT:C | 16M X 32 DDR DRAM, PBGA90 |

| ML1I-65656L-100CB | 32K X 8 STANDARD SRAM, 100 ns, CDIP28 |

| M95160-MB6TP | 2K X 8 SPI BUS SERIAL EEPROM, DSO8 |

| M95160-WMB3T | 2K X 8 SPI BUS SERIAL EEPROM, DSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M95010-WDW5T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:4Kbit, 2Kbit and 1Kbit Serial SPI Bus EEPROM With High Speed Clock |

| M95010-WDW6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:4Kbit, 2Kbit and 1Kbit Serial SPI Bus EEPROM With High Speed Clock |

| M95010-WDW6/W | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:4Kbit, 2Kbit and 1Kbit Serial SPI Bus EEPROM With High Speed Clock |

| M95010-WDW6G | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:4Kbit, 2Kbit and 1Kbit Serial SPI Bus EEPROM With High Speed Clock |

| M95010-WDW6G/W | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:4Kbit, 2Kbit and 1Kbit Serial SPI Bus EEPROM With High Speed Clock |

发布紧急采购,3分钟左右您将得到回复。