- 您现在的位置:买卖IC网 > PDF目录180472 > MACH120-15JC (LATTICE SEMICONDUCTOR CORP) High-Performance EE CMOS Programmable Logic PDF资料下载

参数资料

| 型号: | MACH120-15JC |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | High-Performance EE CMOS Programmable Logic |

| 中文描述: | EE PLD, 15 ns, PQCC68 |

| 封装: | PLASTIC, LCC-68 |

| 文件页数: | 17/20页 |

| 文件大小: | 171K |

| 代理商: | MACH120-15JC |

MACH120-12/15

7

MACH

1

&

2

Families

FUNCTIONAL DESCRIPTION

The MACH120 consists of four PAL blocks connected by a switch matrix. There are 48 I/O pins

and 4 dedicated input pins feeding the switch matrix. These signals are distributed to the four

PAL blocks for efcient design implementation. There are 4 clock pins that can also be used as

dedicated inputs.

The PAL Blocks

Each PAL block in the MACH120 (Figure 1) contains a 48-product-term logic array, a logic allocator,

12 macrocells and 12 I/O cells. The switch matrix feeds each PAL block with 26 inputs. This makes

the PAL block look effectively like an independent “PALCE26V12”.

There are four additional output enable product terms in each PAL block. For purposes of output

enable, the 12 I/O cells are divided into 2 banks of 6 macrocells. Each bank is allocated two of

the output enable product terms.

An asynchronous reset product term and an asynchronous preset product term are provided for

ip-op initialization. All ip-ops within the PAL block are initialized together.

The Switch Matrix

The MACH120 switch matrix is fed by the inputs and feedback signals from the PAL blocks. Each

PAL block provides 12 internal feedback signals and 12 I/O feedback signals. The switch matrix

distributes these signals back to the PAL blocks in an efcient manner that also provides for high

performance. The design software automatically congures the switch matrix when tting a design

into the device.

The Product-Term Array

The MACH120 product-term array consists of 48 product terms for logic use, and 6 special-purpose

product terms. Four of the special-purpose product terms provide programmable output enable, one

provides asynchronous reset, and one provides asynchronous preset. Two of the output enable

product terms are used for the rst six I/O cells; the other two control the last six macrocells.

The Logic Allocator

The logic allocator in the MACH120 takes the 48 logic product terms and allocates them to the

12 macrocells as needed. Each macrocell can be driven by up to 12 product terms. The design

software automatically congures the logic allocator when tting the design into the device.

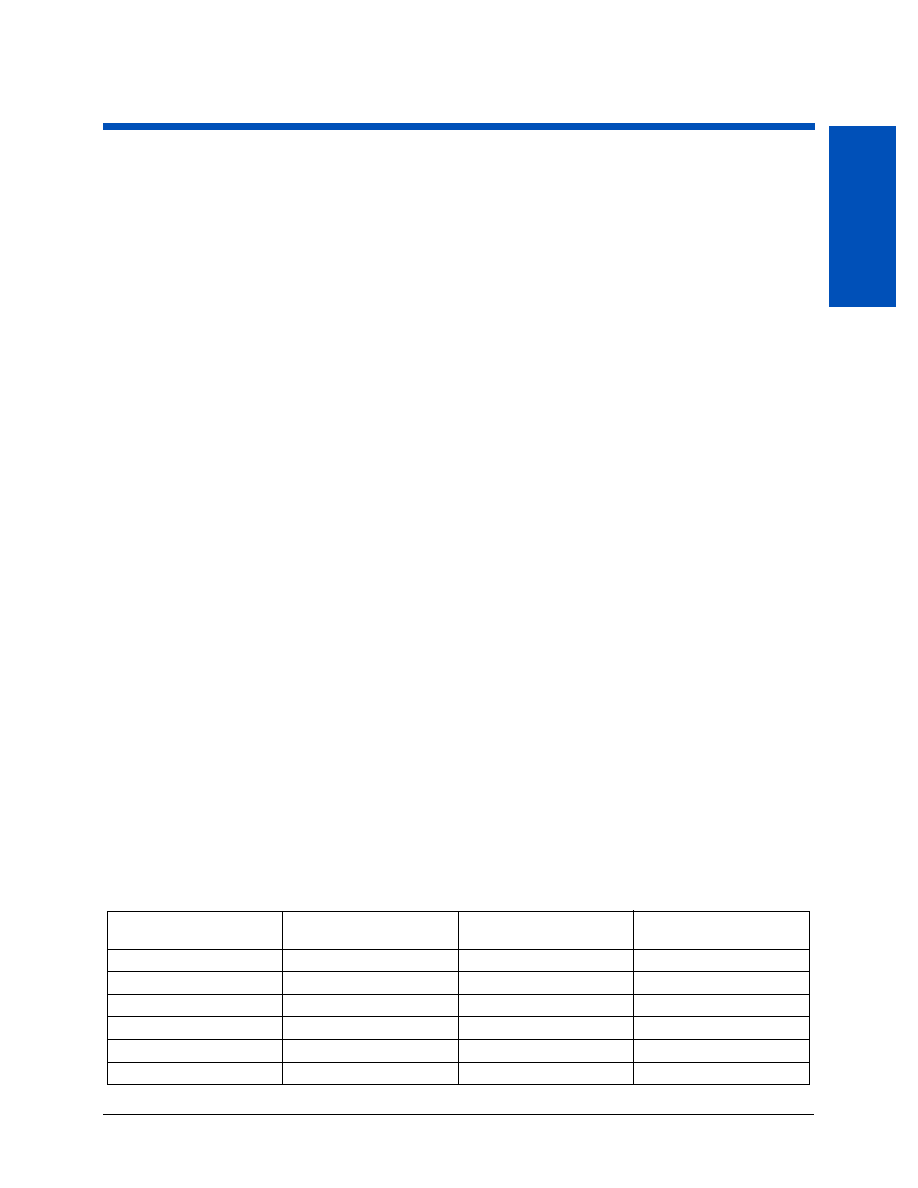

Table 1 illustrates which product term clusters are available to each macrocell within a PAL

block. Refer to Figure 1 for cluster and macrocell numbers.

Table 1.

Logic Allocation

Output Macrocell

Available

Clusters

Output Macrocell

Available

Clusters

M0

C0, C1

M6

C5, C6, C7

M1

C0, C1, C2

M7

C6, C7, C8

M2

C1, C2, C3

M8

C7, C8, C9

M3

C2, C3, C4

M9

C8, C9, C10

M4

C3, C4, C5

M10

C9, C10, C11

M5

C4, C5, C6

M11

C10, C11

相关PDF资料 |

PDF描述 |

|---|---|

| MACH120-12 | High-Performance EE CMOS Programmable Logic |

| MACH131SP-12YC | High-Performance EE CMOS Programmable Logic |

| MACH131SP-15YC | High-Performance EE CMOS Programmable Logic |

| MACH131SP-5YC | High-Performance EE CMOS Programmable Logic |

| MACH131SP-7YC | High-Performance EE CMOS Programmable Logic |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MACH120-15JC-18JI | 制造商:Advanced Micro Devices 功能描述: |

| MACH120-20JC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MACH130-15 | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:High-Density EE CMOS Programmable Logic |

| MACH130-15JC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MACH130-15JC-18JI | 制造商:Advanced Micro Devices 功能描述: |

发布紧急采购,3分钟左右您将得到回复。