- 您现在的位置:买卖IC网 > PDF目录224187 > MAX147AEAP+ (MAXIM INTEGRATED PRODUCTS INC) +2.7V, Low-Power, 8-Channel, Serial 12-Bit ADCs PDF资料下载

参数资料

| 型号: | MAX147AEAP+ |

| 厂商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分类: | ADC |

| 英文描述: | +2.7V, Low-Power, 8-Channel, Serial 12-Bit ADCs |

| 中文描述: | 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| 封装: | SSOP-20 |

| 文件页数: | 28/28页 |

| 文件大小: | 746K |

| 代理商: | MAX147AEAP+ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页

MAX146/MAX147

+2.7V, Low-Power, 8-Channel,

Serial 12-Bit ADCs

_______________________________________________________________________________________

9

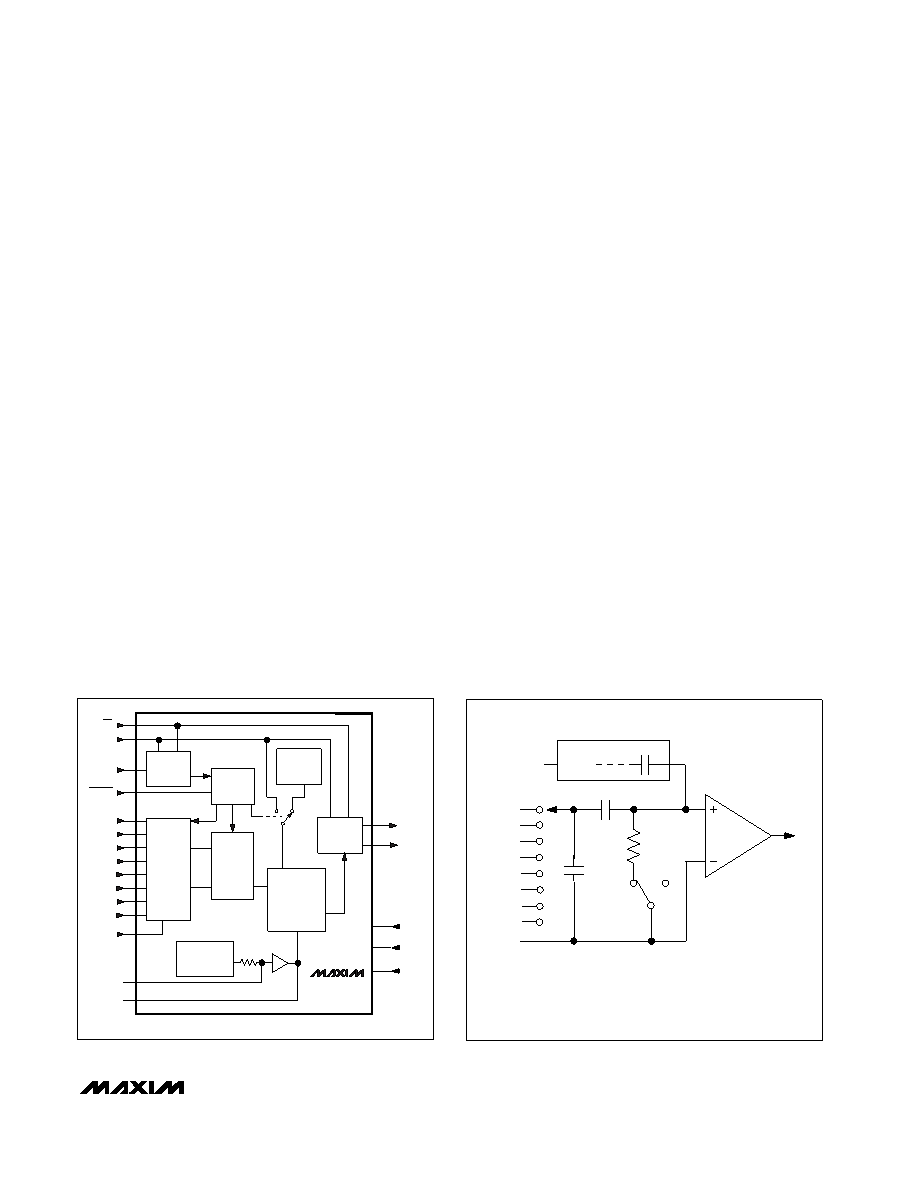

_______________Detailed Description

The MAX146/MAX147 analog-to-digital converters

(ADCs) use a successive-approximation conversion

technique and input track/hold (T/H) circuitry to convert

an analog signal to a 12-bit digital output. A flexible ser-

ial interface provides easy interface to microprocessors

(Ps). Figure 3 is a block diagram of the MAX146/

MAX147.

Pseudo-Differential Input

The sampling architecture of the ADC’s analog com-

parator is illustrated in the equivalent input circuit

(Figure 4). In single-ended mode, IN+ is internally

switched to CH0–CH7, and IN- is switched to COM. In

differential mode, IN+ and IN- are selected from the fol-

lowing pairs: CH0/CH1, CH2/CH3, CH4/CH5, and

CH6/CH7. Configure the channels with Tables 2 and 3.

In differential mode, IN- and IN+ are internally switched

to either of the analog inputs. This configuration is

pseudo-differential to the effect that only the signal at

IN+ is sampled. The return side (IN-) must remain sta-

ble within ±0.5LSB (±0.1LSB for best results) with

respect to AGND during a conversion. To accomplish

this, connect a 0.1F capacitor from IN- (the selected

analog input) to AGND.

During the acquisition interval, the channel selected as

the positive input (IN+) charges capacitor CHOLD. The

acquisition interval spans three SCLK cycles and ends

on the falling SCLK edge after the last bit of the input

control word has been entered. At the end of the acqui-

sition interval, the T/H switch opens, retaining charge

on CHOLD as a sample of the signal at IN+.

The conversion interval begins with the input multiplex-

er switching CHOLD from the positive input (IN+) to the

negative input (IN-). In single-ended mode, IN- is sim-

ply COM. This unbalances node ZERO at the compara-

tor’s input. The capacitive DAC adjusts during the

remainder of the conversion cycle to restore node

ZERO to 0V within the limits of 12-bit resolution. This

action is equivalent to transferring a 16pF x [(VIN+) -

(VIN-)] charge from CHOLD to the binary-weighted

capacitive DAC, which in turn forms a digital represen-

tation of the analog input signal.

Track/Hold

The T/H enters its tracking mode on the falling clock

edge after the fifth bit of the 8-bit control word has been

shifted in. It enters its hold mode on the falling clock

edge after the eighth bit of the control word has been

shifted in. If the converter is set up for single-ended

inputs, IN- is connected to COM, and the converter

samples the “+” input. If the converter is set up for dif-

ferential inputs, IN- connects to the “-” input, and the

difference of

|IN+ - IN-| is sampled. At the end of the

conversion, the positive input connects back to IN+,

and CHOLD charges to the input signal.

INPUT

SHIFT

REGISTER

CONTROL

LOGIC

INT

CLOCK

OUTPUT

SHIFT

REGISTER

+1.21V

REFERENCE

(MAX146)

T/H

ANALOG

INPUT

MUX

12-BIT

SAR

ADC

IN

DOUT

SSTRB

VDD

DGND

AGND

SCLK

DIN

COM

REFADJ

VREF

OUT

REF

CLOCK

+2.500V

20k

*A

≈ 2.00 (MAX147)

10

11

12

9

15

16

17

18

19

CH6

7

CH7

8

CH4

5

CH5

6

CH1

2

CH2

3

CH3

4

CH0

1

MAX146

MAX147

CS

SHDN

20

14

13

≈ 2.06*

A

Figure 3. Block Diagram

CH0

CH1

CH2

CH3

CH4

CH5

CH6

CH7

COM

CSWITCH

TRACK

T/H

SWITCH

RIN

9k

CHOLD

HOLD

12-BIT CAPACITIVE DAC

VREF

ZERO

COMPARATOR

–

+

16pF

SINGLE-ENDED MODE: IN+ = CH0–CH7, IN- = COM.

DIFFERENTIAL MODE: IN+ AND IN- SELECTED FROM PAIRS OF

CH0/CH1, CH2/CH3, CH4/CH5, AND CH6/CH7.

AT THE SAMPLING INSTANT,

THE MUX INPUT SWITCHES

FROM THE SELECTED IN+

CHANNEL TO THE SELECTED

IN- CHANNEL.

INPUT

MUX

Figure 4. Equivalent Input Circuit

相关PDF资料 |

PDF描述 |

|---|---|

| MAX147ACAP+T | +2.7V, Low-Power, 8-Channel, Serial 12-Bit ADCs |

| MAX147ACAP+ | +2.7V, Low-Power, 8-Channel, Serial 12-Bit ADCs |

| MAX146BEPP+ | +2.7V, Low-Power, 8-Channel, Serial 12-Bit ADCs |

| MAX146BEAP+ | +2.7V, Low-Power, 8-Channel, Serial 12-Bit ADCs |

| MAX146BEAP+T | +2.7V, Low-Power, 8-Channel, Serial 12-Bit ADCs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX147AEAP+ | 功能描述:模数转换器 - ADC 12-Bit 8Ch 133ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX147AEAP+T | 功能描述:模数转换器 - ADC 12-Bit 8Ch 133ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX147AEAP-T | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX147AEPP | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX147AEPP+ | 功能描述:模数转换器 - ADC 12-Bit 8Ch 133ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。