- 您现在的位置:买卖IC网 > PDF目录18824 > MAX2870ETJ+ (Maxim Integrated)RF FRACT INTR N SYNTH VCO 32TQFN PDF资料下载

参数资料

| 型号: | MAX2870ETJ+ |

| 厂商: | Maxim Integrated |

| 文件页数: | 14/24页 |

| 文件大小: | 0K |

| 描述: | RF FRACT INTR N SYNTH VCO 32TQFN |

| 标准包装: | 60 |

| 功能: | 小数、整数 N 频率合成器/VCO |

| 频率: | 23.5MHz ~ 6GHz |

| RF 型: | 通用 |

| 封装/外壳: | 32-WFQFN 裸露焊盘 |

| 包装: | 管件 |

�� �

�

�

�MAX2870�

�23.5MHz� to� 6000MHz� Fractional/�

�Integer-N� Synthesizer/VCO�

�The� charge-pump� output� can� be� put� into� high-imped-�

�ance� mode� when� TRI� =� 1� (register� 2,� bit� 4).� The� output� is�

�in� normal� mode� when� TRI� =� 0.�

�The� phase� detector� polarity� can� be� changed� if� an� active�

�inverting� loop� filter� topology� is� used.� For� noninverting�

�loop� filters,� set� PDP� =� 1� (register� 2,� bit� 6).� For� inverting�

�loop� filters,� set� PDP� =� 0.�

�MUX_OUT� and� Lock� Detect�

�MUX_OUT� is� a� multipurpose� test� output� for� observing�

�various� internal� functions� of� the� MAX2870.� MUX_OUT�

�can� also� be� configured� as� serial� data� output.� Bits� MUX�

�(register� 2,� bit� 28:26)� are� used� to� select� the� desired�

�MUX_OUT� signal� (see� Table� 6).�

�Lock� detect� can� be� monitored� through� the� LD� output� by�

�setting� the� LD� bits� (register� 5,� bits� 23:22).� For� digital� lock�

�detect,� set� LD� =� 01.� The� digital� lock� detect� is� dependent�

�on� the� mode� of� the� synthesizer.� In� frac-N� mode� set� LDF�

�=� 0,� and� in� int-N� mode� set� LDF� =� 1.� To� set� the� accuracy�

�of� the� digital� lock� detect,� see� Tables� 1� and� 2.�

�Analog� lock� detect� can� be� set� with� LD� =� 10.� In� this� mode,�

�LD� is� an� open-drain� output� and� requires� an� external�

�pullup� resistor.�

�Fast-Lock�

�The� device� uses� a� fast-lock� mode� to� decrease� lock� time.�

�This� mode� requires� that� CP� =� 0000� (register� 2,� bits� 12:9)�

�and� that� the� shunt� resistive� portion� of� the� loop� filter� be�

�segmented� into� two� parts,� where� one� resistor� is� 1/4th�

�the� total� resistance,� and� the� other� resistor� is� 3/4th� the�

�total� resistance.� The� larger� resistor� should� be� connected�

�from� ground� to� SW,� and� the� smaller� resistor� from� SW� to�

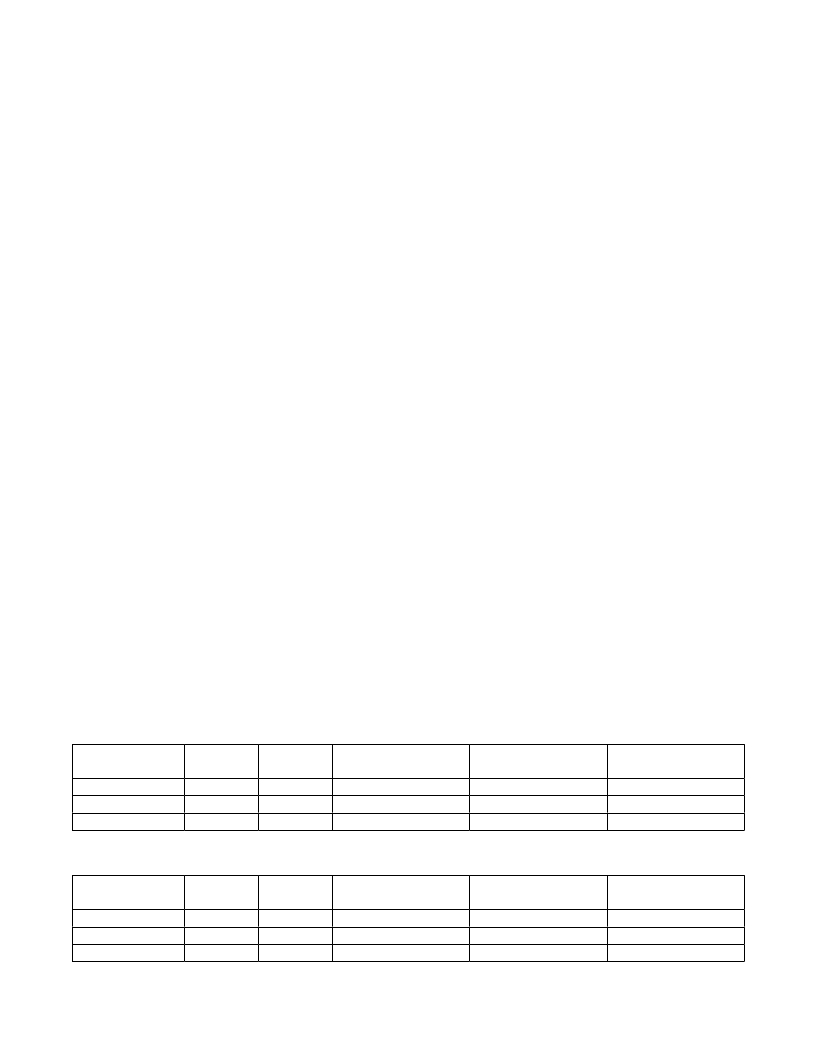

�Table 1. Frac-N� Digital� Lock-Detect� Settings�

�the� loop� filter� capacitor.� When� CDM� =� 01� (register� 3,� bits�

�16:15),� fast-lock� is� active� after� the� VAS� has� completed.�

�During� fast-lock,� the� charge� pump� is� increased� to� CP� =�

�1111� and� the� shunt� loop� filter� resistance� is� set� to� 1/4th�

�the� total� resistance� by� changing� pin� SW� from� high� imped-�

�ance� to� ground.� Fast-lock� deactivates� after� a� timeout� set�

�by� the� user.� This� timeout� is� loop� filter� dependent,� and� is�

�set� by:�

�t� FAST-LOCK� =� M� x� CDIV/f� PFD�

�where� M� is� the� modulus� setting� and� CDIV� is� the� clock�

�divider� setting.� The� user� must� determine� the� CDIV� setting�

�based� on� their� loop� filter� time� constant.�

�RFOUTA±� and� RFOUTB±�

�The� device� has� dual� differential� open-collector� RF� out-�

�puts� that� require� an� external� RF� choke� 50� I� resistor� to�

�supply� for� each� output.� Each� differential� output� can�

�be� independently� enabled� or� disabled� by� setting� bits�

�RFA_EN� (register� 4,� bit� 5)� and� RFB_EN� (register� 4,� bit� 8).�

�Both� outputs� are� also� controlled� by� applying� a� logic-high�

�(enabled)� or� logic-low� (disabled)� to� pin� RFOUT_EN.�

�The� output� power� of� each� output� can� be� individually�

�controlled� with� APWR� (register� 4,� bits� 4:3)� for� RFOUTA�

�and� BPWR� (register� 4,� bits� 7:6)� for� RFOUTB.� The� avail-�

�able� differential� output� power� settings� are� from� -4dBm�

�to� +5dBm,� in� 3dB� steps� with� 50� I� pullup� to� supply.� The�

�available� single-ended� output� power� ranges� from� -4dBm�

�to� +5dBm� in� 3dB� steps� with� a� RF� choke� to� supply.� Across�

�the� entire� frequency� range� different� pullup� elements� (L�

�or� R)� are� required� for� optimal� output� power.� If� the� output�

�is� used� single� ended,� the� unused� output� should� be� termi-�

�nated� in� a� corresponding� load.�

�PFD� FREQUENCY�

�P� 32MHz�

�P� 32MHz�

�>� 32MHz�

�LDS�

�0�

�0�

�1�

�LDP�

�0�

�1�

�X�

�LOCKED� UP/DOWN�

�TIME� SKEW� (ns)�

�10�

�6�

�4�

�NUMBER� OF� LOCKED�

�CYCLES� TO� SET� LD�

�40�

�40�

�40�

�UP/DOWNTIME� SKEW�

�TO� UNSET� LD� (ns)�

�15�

�15�

�4�

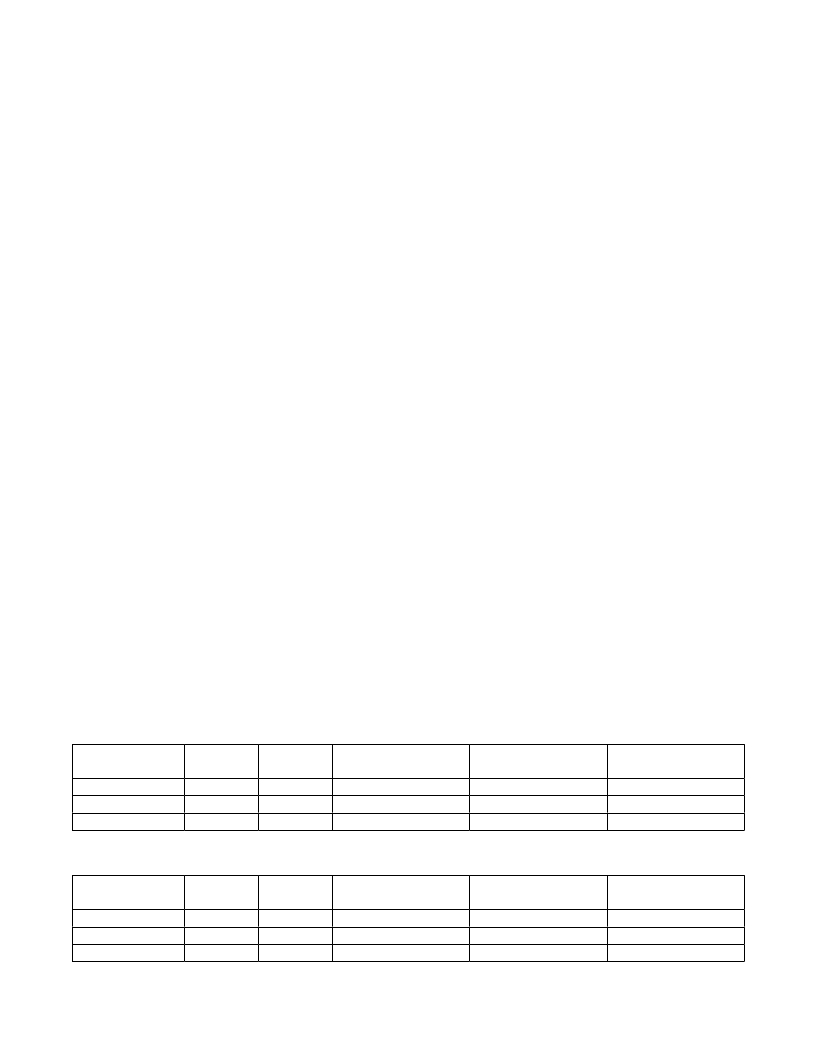

�Table� 2.� Int-N� Digital� Lock-Detect� Settings�

�PFD� FREQUENCY�

�P� 32MHz�

�P� 32MHz�

�>� 32MHz�

�LDS�

�0�

�0�

�1�

�LDP�

�0�

�1�

�X�

�LOCKED� UP/DOWN�

�TIME� SKEW� (ns)�

�10�

�6�

�4�

�NUMBER� OF� LOCKED�

�CYCLES� TO� SET� LD�

�5�

�5�

�5�

�UP/DOWNTIME� SKEW�

�TO� UNSET� LD� (ns)�

�15�

�15�

�4�

�Maxim� Integrated�

�14�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX1385BETM+ | IC CTRLR LDMOS BIAS 5V 48-TQFN |

| T620063004DN | SCR PHASE CTRL MOD 600V 300A |

| MAX2023ETX+ | IC MOD/DEMOD HI DYN RNG 36-TQFN |

| MAX2021ETX+ | IC MOD/DEMOD 36-TQFN |

| T620042004DN | SCR PHASE CTRL MOD 400V 200A |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX2870ETJ+ | 功能描述:锁相环 - PLL PLL/VCO RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| MAX2870ETJ+T | 功能描述:锁相环 - PLL PLL/VCO RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| MAX2870EVKIT# | 功能描述:射频开发工具 MAX2870 Eval Kit RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| MAX2880ETP+ | 制造商:Maxim Integrated Products 功能描述:12.4GHZ HIGH PERFORMANCE FRACTIONAL/INTEGER-N SYNTHESIZER - Rail/Tube 制造商:Maxim Integrated Products 功能描述:RF FRACT INTEGER N SYNTH QFN |

| MAX2880ETP+T | 制造商:Maxim Integrated Products 功能描述:RF FRACT INTEGER N SYNTH QFN |

发布紧急采购,3分钟左右您将得到回复。