- 您现在的位置:买卖IC网 > PDF目录18824 > MAX2870ETJ+ (Maxim Integrated)RF FRACT INTR N SYNTH VCO 32TQFN PDF资料下载

参数资料

| 型号: | MAX2870ETJ+ |

| 厂商: | Maxim Integrated |

| 文件页数: | 15/24页 |

| 文件大小: | 0K |

| 描述: | RF FRACT INTR N SYNTH VCO 32TQFN |

| 标准包装: | 60 |

| 功能: | 小数、整数 N 频率合成器/VCO |

| 频率: | 23.5MHz ~ 6GHz |

| RF 型: | 通用 |

| 封装/外壳: | 32-WFQFN 裸露焊盘 |

| 包装: | 管件 |

�� �

�

�

�MAX2870�

�23.5MHz� to� 6000MHz� Fractional/�

�Integer-N� Synthesizer/VCO�

�Voltage-Controlled� Oscillator�

�The� fundamental� VCO� frequency� of� the� device� guarantees�

�gap-free� coverage� from� 3.0GHz� to� 6.0GHz� using� four�

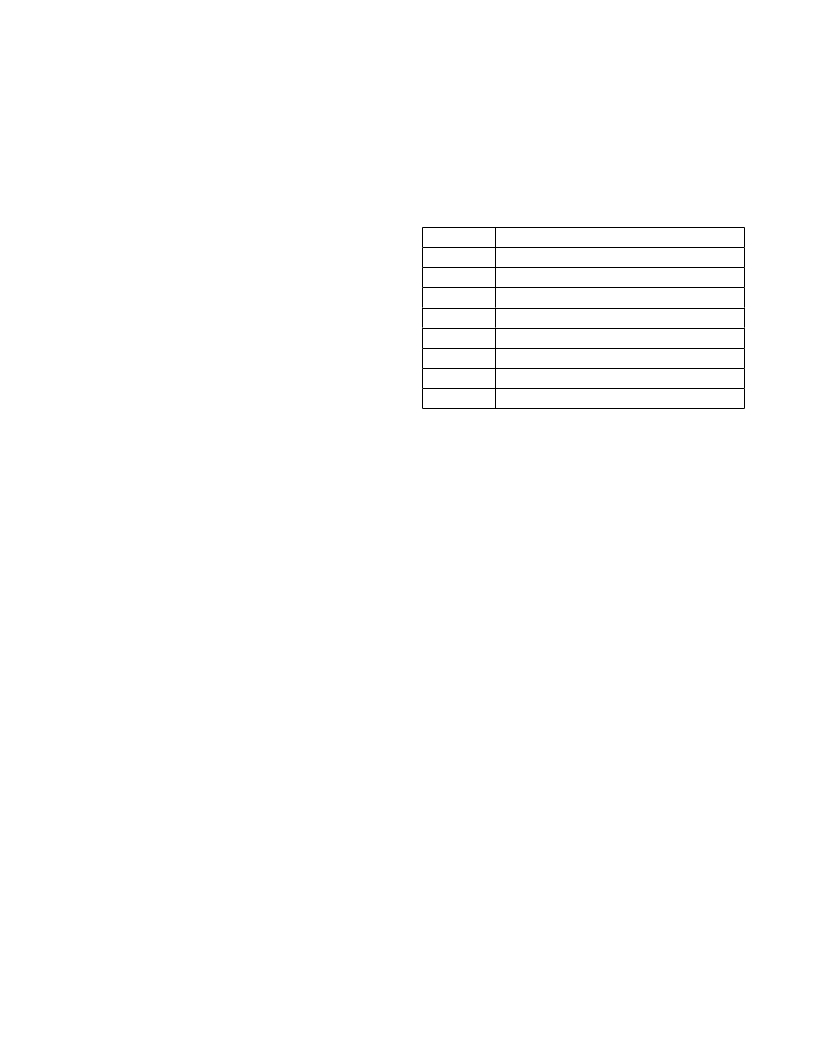

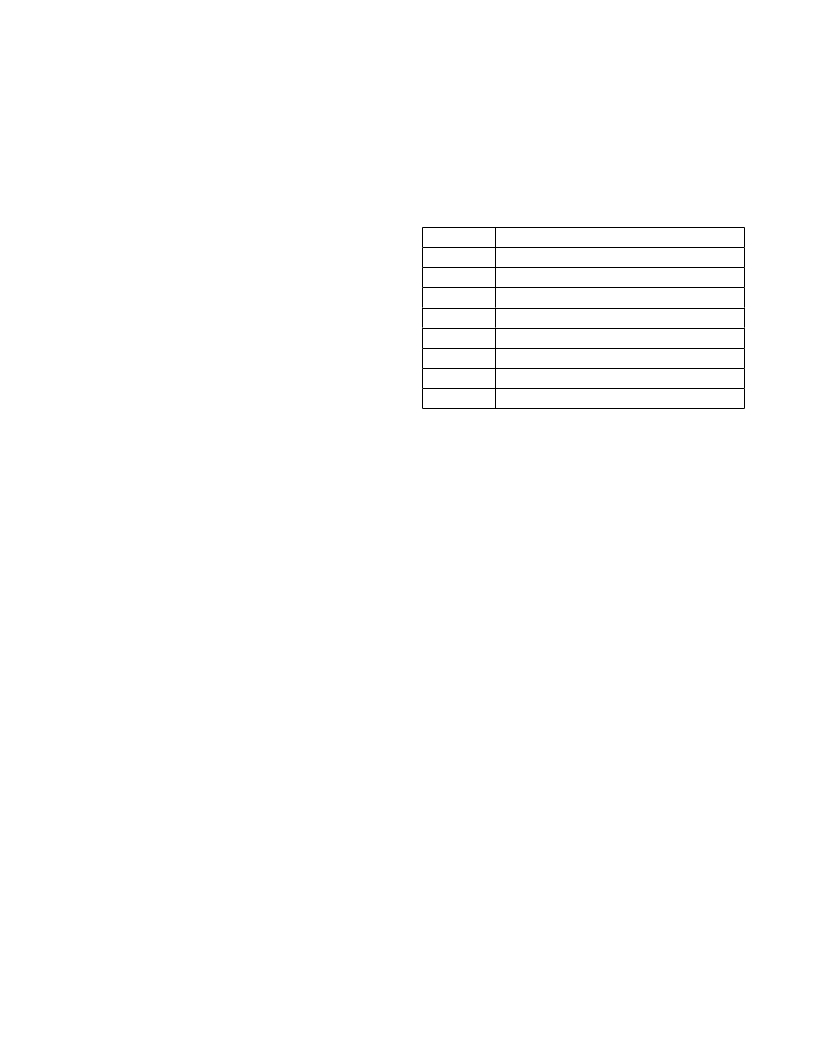

�Table� 3.� ADC� VCO� Status�

�ADC� VCO� STATUS�

�individual� VCO� core� blocks� with� 16� sub-bands� within�

�each� block.� Connect� the� output� of� the� loop� filter� to� the�

�TUNE� input.� The� TUNE� input� is� used� to� control� the� VCO.�

�Tune� ADC�

�A� 3-bit� ADC� is� used� to� read� the� VCO� tuning� voltage.� The�

�ADC� value� can� be� read� back� by� bits� 22:20� in� register� 6.�

�The� ADC� uses� the� ranges� shown� in� Table� 3.�

�Note� that� the� digital� or� analog� lock� detect� might� still� be�

�valid� when� the� tuning� voltage� is� out� of� the� compliance�

�range.�

�000�

�001�

�010�

�011�

�100�

�101�

�110�

�111�

�Out-of-lock,� V� TUNE� <� 0.5V�

�In-lock,� 0.5V� <� V� TUNE� <� 0.7V�

�In-lock,� 0.7V� <� V� TUNE� <� 1.3V�

�Not� used�

�Not� used�

�In-lock,� 1.3V� <� V� TUNE� <� 2.1V�

�In-lock,� 2.1V� <� V� TUNE� <� 2.5V�

�Out-of-lock,� V� TUNE� >� 2.5V�

�VCO� Autoselect� (VAS)� State� Machine�

�An� internal� VCO� autoselect� state� machine� is� initiated�

�when� register� 0� is� programmed� to� automatically� select�

�the� correct� VCO� if� bit� VAS_SHDN� =� 0� (register� 3,� bit� 25).� If�

�VAS_SHDN� =� 1,� then� the� VCO� can� be� manually� selected�

�by� bits� VCO.�

�The� state� machine� clock,� f� BS� ,� must� be� set� to� 50kHz.� This�

�is� set� by� the� BS� bits.� The� formula� for� setting� BS� is:�

�BS� =� f� PFD� /50kHz�

�where� f� PFD� is� the� phase-detector� frequency.� The� BS� (regis-�

�ter� 4,� bits� 19:12)� value� should� be� rounded� to� the� nearest�

�integer.� If� the� calculated� BS� is� higher� than� 1023,� then� set�

�BS� =� 1023.� If� f� PFD� is� lower� than� 50kHz,� then� set� BS� =� 1.�

�The� time� needed� to� select� the� correct� VCO� is� 10/f� BS� .�

�The� RETUNE� (register� 3,� bit� 24)� bit� is� used� to� enable� or�

�disable� the� VAS� auto-retune� function.� Should� the� 3-bit�

�TUNE� ADC� detect� that� the� VCO� control� voltage� (V� TUNE� )�

�has� drifted� into� the� 000� or� 111� state,� the� VAS� will� initiate�

�an� auto-retune� if� RETUNE� =� 1.� If� RETUNE� =� 0,� then� this�

�function� is� disabled.�

�Maxim� Integrated�

�Phase� Shift� Mode�

�After� achieving� lock,� the� phase� of� the� RF� output� can�

�be� changed� in� increments� of� P/M� x� 360� N� .� The� absolute�

�phase� cannot� be� determined,� but� it� can� be� changed�

�relative� to� the� current� phase.�

�To� change� the� phase,� do� the� following:�

�1)� Achieve� lock� at� the� desired� frequency.�

�2)� Set� the� increment� of� phase� relative� to� the� current� phase�

�by� setting� P� =� M� x� {desired_phase_change}/360� N� .�

�3)� Enable� the� phase� change� by� setting� CDM� =� 10.�

�4)� Reset� CDM� =� 00.�

�Low-Spur� Mode�

�The� device� offers� three� modes� for� the� sigma-delta� modu-�

�lator.� Low-noise� mode� offers� lower� in-band� noise� at� the�

�expense� of� spurs.� The� spurs� can� be� reduced� by� setting�

�SDN� =� 10� (register� 2,� bits� 30:29)� or� SDN� =� 11� for� different�

�modes� of� dithering.� The� user� can� determine� which� mode�

�works� best� for� their� application.�

�15�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX1385BETM+ | IC CTRLR LDMOS BIAS 5V 48-TQFN |

| T620063004DN | SCR PHASE CTRL MOD 600V 300A |

| MAX2023ETX+ | IC MOD/DEMOD HI DYN RNG 36-TQFN |

| MAX2021ETX+ | IC MOD/DEMOD 36-TQFN |

| T620042004DN | SCR PHASE CTRL MOD 400V 200A |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX2870ETJ+ | 功能描述:锁相环 - PLL PLL/VCO RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| MAX2870ETJ+T | 功能描述:锁相环 - PLL PLL/VCO RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| MAX2870EVKIT# | 功能描述:射频开发工具 MAX2870 Eval Kit RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| MAX2880ETP+ | 制造商:Maxim Integrated Products 功能描述:12.4GHZ HIGH PERFORMANCE FRACTIONAL/INTEGER-N SYNTHESIZER - Rail/Tube 制造商:Maxim Integrated Products 功能描述:RF FRACT INTEGER N SYNTH QFN |

| MAX2880ETP+T | 制造商:Maxim Integrated Products 功能描述:RF FRACT INTEGER N SYNTH QFN |

发布紧急采购,3分钟左右您将得到回复。