- 您现在的位置:买卖IC网 > PDF目录1938 > MAX3107EAG+ (Maxim Integrated Products)IC UART SPI/I2C 128 FIFO 24SSOP PDF资料下载

参数资料

| 型号: | MAX3107EAG+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 7/52页 |

| 文件大小: | 0K |

| 描述: | IC UART SPI/I2C 128 FIFO 24SSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 58 |

| 特点: | 内部振荡器 |

| 通道数: | 4,QUART |

| FIFO's: | 128 字节 |

| 规程: | RS232,RS485 |

| 电源电压: | 2.35 V ~ 3.6 V |

| 带自动流量控制功能: | 是 |

| 带IrDA 编码器/解码器: | 是 |

| 带故障启动位检测功能: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-SSOP(0.209",5.30mm 宽) |

| 供应商设备封装: | 24-SSOP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

SPI/I2C UART with 128-Word FIFOs

Detailed Description

The MAX3107 UART is a bridge between an SPI/

MICROWIRE or I2C microprocessor bus and an

asynchronous serial-data communication link, such as

RS-485, RS-232, or IrDA. The MAX3107 contains an

advanced UART, a fractional baud-rate generator, and

four GPIOs. The MAX3107 is configured and monitored,

and data is written and read from 8-bit registers through

SPI or I2C. These registers are organized by related

function as shown in the Register Map.

The host controller loads data into the Transmit Holding

register (THR) through SPI or I2C. This data is automati-

cally pushed into the transmit FIFO and sent out at TX.

The MAX3107 adds START, STOP, and parity bits to

the data and sends the data out at the selected baud

rate. The clock configuration registers determine the

baud rate, clock source selection, and clock frequency

prescaling.

The receiver in the MAX3107 detects a START bit as a

high-to-low RX transition. An internal clock samples this

data. The received data is automatically placed in the

receive FIFO and can then be read out of the RxFIFO

through the RHR.

Register Set

The MAX3107 has a flat register structure without shad-

ow registers. The registers are 8 bits wide. The MAX3107

registers have some similarities to the 16C550 registers.

Receive and Transmit FIFOs

The UART’s receiver and the transmitter each have a

128-word deep FIFO, reducing the intervals that the host

processor needs to dedicate for high-speed, high-vol-

ume data transfer. As the data rates of the asynchronous

RX, TX interfaces increase and get closer to those of the

host controller’s SPI/I2C data rates, UART management

and flow control can make up a significant portion of the

host’s activity. By increasing FIFO size, the host is inter-

rupted less often and can utilize SPI/I2C burst data block

transfers to/from the FIFOs.

FIFO trigger levels can generate interrupts to the host

controller, signaling that programmed FIFO fill levels

have been reached. The transmitter and receiver trig-

ger levels are programmed through FIFOTrgLvl with a

resolution of eight FIFO locations. When a receive FIFO

trigger is generated, the host knows that the receive

FIFO has a defined number of words waiting to be read

out or that a known number of vacant FIFO locations are

available and ready to be filled. The transmit FIFO trig-

ger generates an interrupt when the transmit FIFO level

is above the programmed trigger level. The host then

knows to throttle data writing to the transmit FIFO.

The host can read out the number of words present in each

of the FIFOs through the TxFIFOLvl and RxFIFOLvl registers.

Transmitter Operation

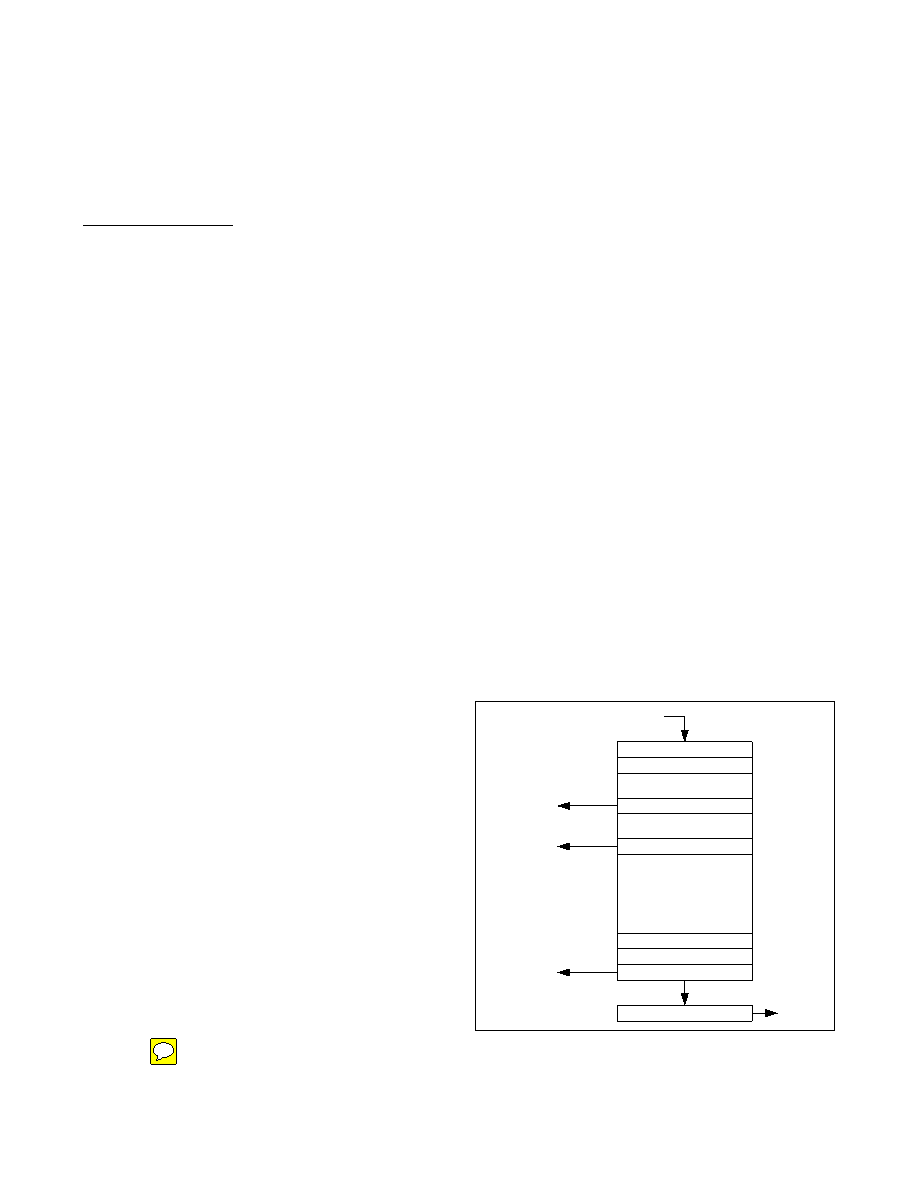

Figure 3 shows the structure of the transmitter with the

TxFIFO. The transmit FIFO can hold up to 128 words that

are written to it through THR.

The current number of words in the TxFIFO can be read

out through the TxFIFOLvl register. The transmit FIFO

can be programmed to generate an interrupt when a

programmed number of words are present in the TxFIFO

through the FIFOTrgLvl register. The TxFIFO interrupt

trigger level is selectable through FIFOTrgLvl[3:0]. When

the transmit FIFO fill level reaches the programmed trig-

ger level, the ISR[4] interrupt is set.

The transmit FIFO is empty when ISR[5]: TxEmtyInt is set.

ISR[5] turns high when the transmitter starts transmit-

ting the last word in the TxFIFO. Hence, the transmitter

is completely empty after ISR[5] is set with an addi-

tional delay equal to the length of a complete character

(including START, parity, and STOP bits).

The contents of the TxFIFO and RxFIFOs are both

cleared through MODE2[1]: FIFORst.

Figure 3. Transmit FIFO Signals

MICROWIRE is a trademark of National Semiconductor Corp.

CURRENT FILL LEVEL

TRANSMITTER

TX

TRANSMIT FIFO

FIFOTrgLvl[3:0]

TRIGGER

ISR[4]

THR

DATA FROM SPI/I2C INTERFACE

128

3

2

1

LEVEL

TxFIFOLvl

EMPTY

ISR[5]

Maxim Integrated

15

MAX3107

相关PDF资料 |

PDF描述 |

|---|---|

| MAX3108EWA+T | IC UART |

| MAX3109ETJ+ | SEMICONDUCTOR OTHER |

| MAX310CPE | IC VIDEO MULTIPLEXER 8X1 16DIP |

| MAX3110EENI+G36 | IC UART SPI COMPAT 28-DIP |

| MAX3120CUA+ | IC TXRX INFRARED IRDA 8-UMAX |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX3107EAG+ | 功能描述:UART 接口集成电路 SPI/I2C Compatible RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| MAX3107EAG+T | 功能描述:UART 接口集成电路 SPI/I2C Compatible RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| MAX3107ETG/V+ | 功能描述:UART 接口集成电路 UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| MAX3107ETG/V+T | 功能描述:UART 接口集成电路 SPI/IC UART with 128-Word FIFOs and Internal Oscillator RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| MAX3107ETG+ | 功能描述:UART 接口集成电路 SPI/I2C Compatible RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。