- 您现在的位置:买卖IC网 > PDF目录2011 > MAX5864ETM+T (Maxim Integrated Products)IC ANLG FRONT END 22MSPS 48-TQFN PDF资料下载

参数资料

| 型号: | MAX5864ETM+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 22/26页 |

| 文件大小: | 0K |

| 描述: | IC ANLG FRONT END 22MSPS 48-TQFN |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 位数: | 10 |

| 通道数: | 4 |

| 功率(瓦特): | 2.10W |

| 电压 - 电源,模拟: | 2.7 V ~ 3.3 V |

| 电压 - 电源,数字: | 1.8 V ~ 3.3 V |

| 封装/外壳: | 48-WFQFN 裸露焊盘 |

| 供应商设备封装: | 48-TQFN-EP(7x7) |

| 包装: | 带卷 (TR) |

MAX5864

Ultra-Low-Power, High Dynamic-

Performance, 22Msps Analog Front End

_______________________________________________________________________________________

5

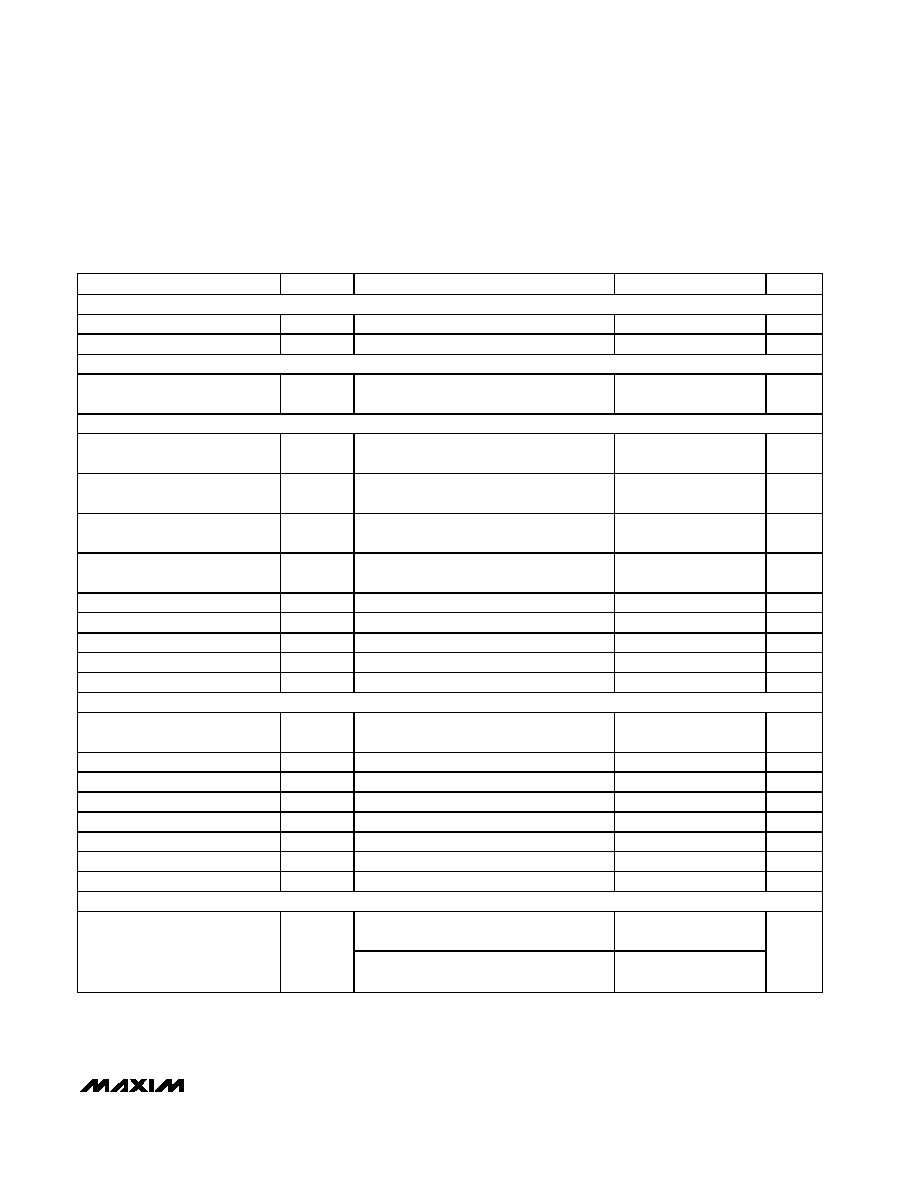

ELECTRICAL CHARACTERISTICS (continued)

(VDD = 3V, OVDD = 1.8V, internal reference (1.024V), CL

≈ 10pF on all digital outputs, fCLK = 22MHz, ADC input amplitude = -0.5dBFS,

DAC output amplitude = 0dBFS, differential ADC input, differential DAC output, CREFP = CREFN = CCOM = 0.33F, Xcvr mode, unless

otherwise noted. Typical values are at TA = +25

°C, unless otherwise noted.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

DAC ANALOG OUTPUT

Full-Scale Output Voltage

VFS

±400

mV

Output Common-Mode Range

1.29

1. 5

V

ADC-DAC INTERCHANNEL CHARACTERISTICS

ADC-DAC Isolation

ADC fINI = fINQ = 5.5MHz, DAC fOUTI =

fOUTQ = 2.2MHz, fCLK = 22MHz

75

dB

ADC-DAC TIMING CHARACTERISTICS

CLK Rise to I-ADC Channel-I

Output Data Valid

tDOI

Figure 3 (Note 4)

7.4

9

ns

CLK Fall to Q-ADC Channel-Q

Output Data Valid

tDOQ

Figure 3 (Note 4)

6.9

9

ns

I-DAC Data to CLK Fall Setup

Time

tDSI

Figure 4 (Note 4)

10

ns

Q-DAC Data to CLK Rise Setup

Time

tDSQ

Figure 4 (Note 4)

10

ns

CLK Fall to I-DAC Data Hold Time

tDHI

Figure 4 (Note 4)

0

ns

CLK Rise to Q-DAC Data Hold Time

tDHQ

Figure 4 (Note 4)

0

ns

Clock Duty Cycle

50

%

CLK Duty-Cycle Variation

±15

%

Digital Output Rise/Fall Time

20% to 80%

2.6

ns

SERIAL INTERFACE TIMING CHARACTERISTICS

Falling Edge of CS to Rising Edge

of First SCLK Time

tCSS

Figure 5 (Note 4)

10

ns

DIN to SCLK Setup Time

tDS

Figure 5 (Note 4)

10

ns

DIN to SCLK Hold Time

tDH

Figure 5 (Note 4)

0

ns

SCLK Pulse Width High

tCH

Figure 5 (Note 4)

25

ns

SCLK Pulse Width Low

tCL

Figure 5 (Note 4)

25

ns

SCLK Period

tCP

Figure 5 (Note 4)

50

ns

SCLK to CS Setup Time

tCS

Figure 5 (Note 4)

0

ns

CS High Pulse Width

tCSW

Figure 5 (Note 4)

80

ns

MODE RECOVERY TIMING CHARACTERISTICS

From shutdown to Rx mode, Figure 6, ADC

settles to within 1dB

20

Shutdown Wake-Up Time

tWAKE,SD

From shutdown to Tx mode, Figure 6, DAC

settles to within 1 LSB error

40

s

相关PDF资料 |

PDF描述 |

|---|---|

| MAX5865ETM+T | IC ANLG FRONT END 40MSPS 48-TQFN |

| MAX5866ETM+ | IC ANLG FRONT END 60MSPS 48-TQFN |

| MAX5873EGK+D | IC DAC 12BIT 200MSPS DUAL 68-QFN |

| MAX5874EGK+D | IC DAC 14BIT 200MSPS DUAL 68-QFN |

| MAX5875EGK+D | IC DAC 16BIT DUAL 200MSPS 68-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX5865ETM | 功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 转换速率: 分辨率:8 bit 接口类型:SPI 电压参考: 电源电压-最大:3.6 V 电源电压-最小:2 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-40 |

| MAX5865ETM+ | 功能描述:ADC / DAC多通道 10-Bit 2Ch 40Msps CODEC/AFE RoHS:否 制造商:Texas Instruments 转换速率: 分辨率:8 bit 接口类型:SPI 电压参考: 电源电压-最大:3.6 V 电源电压-最小:2 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-40 |

| MAX5865ETM+T | 功能描述:ADC / DAC多通道 10-Bit 2Ch 40Msps CODEC/AFE RoHS:否 制造商:Texas Instruments 转换速率: 分辨率:8 bit 接口类型:SPI 电压参考: 电源电压-最大:3.6 V 电源电压-最小:2 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-40 |

| MAX5865ETM-D | 制造商:Maxim Integrated Products 功能描述:DUAL 10BIT DAC & DUAL 8BIT ADC 40MSPS CODEC - Rail/Tube |

| MAX5865ETM-T | 功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 转换速率: 分辨率:8 bit 接口类型:SPI 电压参考: 电源电压-最大:3.6 V 电源电压-最小:2 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-40 |

发布紧急采购,3分钟左右您将得到回复。