- 您现在的位置:买卖IC网 > PDF目录11687 > MAX9218ETM+T (Maxim Integrated Products)IC DESERIALIZER LVDS 48-TQFN PDF资料下载

参数资料

| 型号: | MAX9218ETM+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 4/15页 |

| 文件大小: | 0K |

| 描述: | IC DESERIALIZER LVDS 48-TQFN |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 功能: | 解串器 |

| 数据速率: | 700Mbps |

| 输入类型: | LVDS |

| 输出类型: | LVCMOS |

| 输入数: | 1 |

| 输出数: | 27 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-WFQFN 裸露焊盘 |

| 供应商设备封装: | 48-TQFN-EP(6x6) |

| 包装: | 带卷 (TR) |

MAX9218

27-Bit, 3MHz-to-35MHz

DC-Balanced LVDS Deserializer

12

______________________________________________________________________________________

Input Frequency Detection

A frequency-detection circuit detects when the LVDS

input is not switching. When not switching, all outputs

except LOCK are low, LOCK is high, and PCLK_OUT

follows REFCLK. This condition occurs, for example, if

the serializer is not driving the interconnect or if the

interconnect is open.

Frequency Range Setting (RNG[1:0])

The RNG[1:0] inputs select the operating frequency

range of the MAX9218 and the transition time of the out-

puts. Select the frequency range that includes the

MAX9217 serializer PCLK_IN frequency. Table 3 shows

the selectable frequency ranges and the corresponding

data rates and output transition times.

Power Down

Driving PWRDWN low puts the outputs in high imped-

ance and stops the PLL. With PWRDWN

≤ 0.3V and all

LVTTL/LVCMOS inputs

≤ 0.3V or ≥ VCC - 0.3V, the sup-

ply current is reduced to less than 50A. Driving

PWRDWN high initiates lock to the local reference clock

(REFCLK) and afterwards to the serial input.

Lock and Loss of Lock (LOCK)

When PWRDWN is driven high, the PLL begins locking

to REFCLK, drives LOCK from high impedance to high

and the other outputs from high impedance to low

except PCLK_OUT. PCLK_OUT outputs REFCLK while

the PLL is locking to REFCLK. Locking to REFCLK

takes a maximum of 16,385 REFCLK cycles. When

locking to REFCLK is complete, the serial input is moni-

tored for a transition word. When a transition word is

found, LOCK is driven low indicating valid output data,

and the parallel rate clock recovered from the serial

input is output on PCLK_OUT. PCLK_OUT is stretched

on the change from REFCLK to recovered clock (or

vice versa).

If a transition word is not detected within 220 cycles of

PCLK_OUT, LOCK is driven high and the other outputs

except PCLK_OUT are driven low. REFCLK is output on

PCLK_OUT and the deserializer continues monitoring

the serial input for a transition word. See Figure 7 for

the synchronization timing diagram.

Output Enable (OUTEN) and

Busing Outputs

The outputs of two MAX9218s can be bused to form a

2:1 mux with the outputs controlled by the output

enable. Wait 30ns between disabling one deserializer

(driving OUTEN low) and enabling the second one (dri-

ving OUTEN high) to avoid contention of the bused out-

puts. OUTEN controls all outputs.

Rising or Falling Output Latch Edge (R/F)

The MAX9218 has a selectable rising or falling output

latch edge through a logic setting on R/F. Driving R/F

high selects the rising output latch edge, which latches

the parallel output data into the next chip on the rising

edge of PCLK_OUT. Driving R/F low selects the falling

output latch edge, which latches the parallel output

data into the next chip on the falling edge of

PCLK_OUT. The MAX9218 output-latch-edge polarity

does not need to match the MAX9217 serializer input-

latch-edge polarity. Select the latch-edge polarity

required by the chip being driven by the MAX9218.

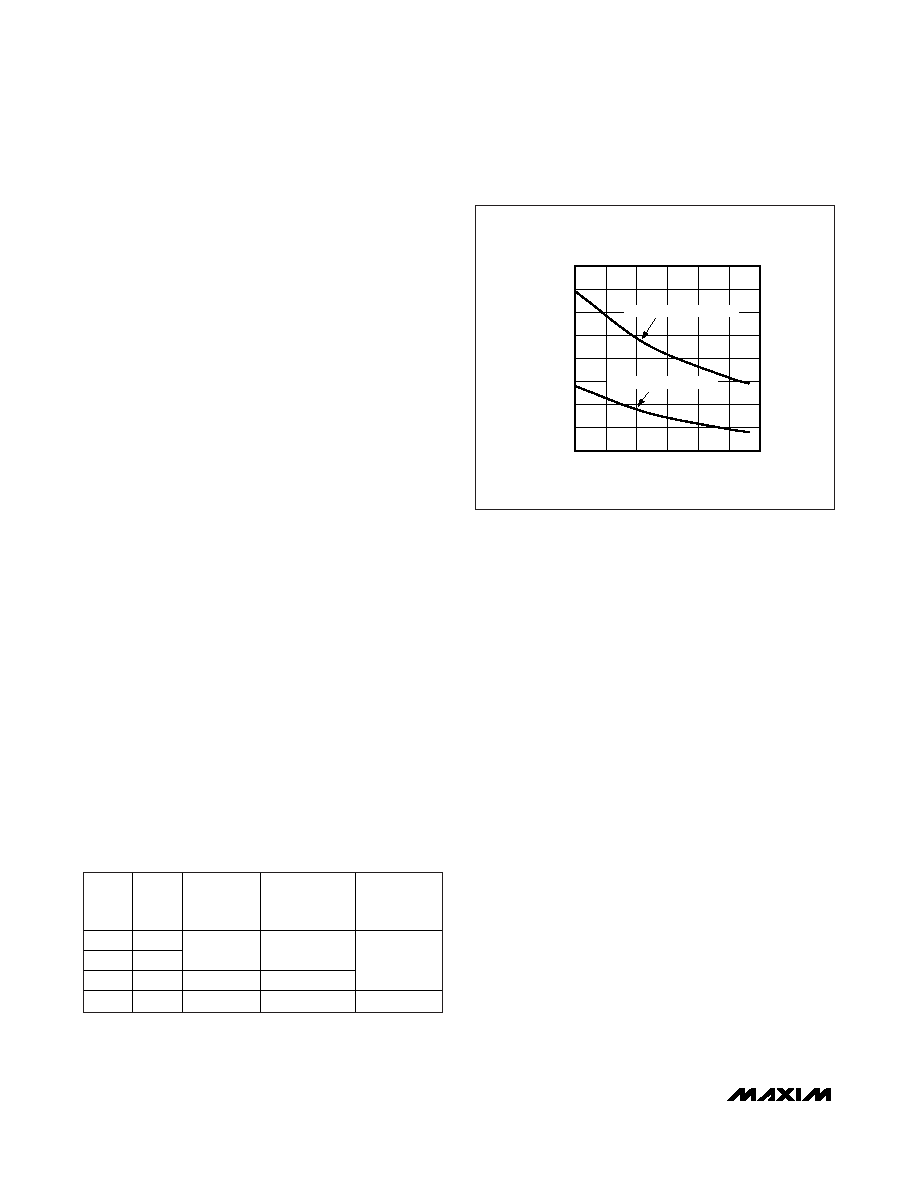

AC-COUPLING CAPACITOR VALUE

vs. PARALLEL CLOCK FREQUENCY

PARALLEL CLOCK FREQUENCY (MHz)

CAPACITOR

VALUE

(nF)

33

30

21

24

27

35

50

65

80

95

110

125

140

20

18

36

TWO CAPACITORS PER LINK

FOUR CAPACITORS PER LINK

RNG1

RNG0

PARALLEL

CLOCK

(MHz)

SERIAL

DATA RATE

(Mbps)

OUTPUT

TRANSITION

TIME

00

01

3 to 7

60 to 140

1

0

7 to 15

140 to 300

Slow

1

15 to 35

300 to 700

Fast

Figure 12. AC-Coupling Capacitor Values vs. Clock Frequency

of 18MHz to 35MHz

Table 3. Frequency Range Programming

相关PDF资料 |

PDF描述 |

|---|---|

| MAX9250ECM+T | IC DESERIALIZER LVDS 48-LQFP |

| MAX9260GCB/V+T | IC DESERIALIZER GMSL 64TQFP |

| MAX9259GCB/V+T | IC SERIALIZER GMSL 64TQFP |

| MAX9217ETM+T | IC SERIALIZER LVDS 48-TQFN |

| VI-B1X-IW-F1 | CONVERTER MOD DC/DC 5.2V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9218EVKIT+ | 功能描述:界面开发工具 MAX9217/18 Eval Kit RoHS:否 制造商:Bourns 产品:Evaluation Boards 类型:RS-485 工具用于评估:ADM3485E 接口类型:RS-485 工作电源电压:3.3 V |

| MAX921C/D | 功能描述:校验器 IC RoHS:否 制造商:STMicroelectronics 产品: 比较器类型: 通道数量: 输出类型:Push-Pull 电源电压-最大:5.5 V 电源电压-最小:1.1 V 补偿电压(最大值):6 mV 电源电流(最大值):1350 nA 响应时间: 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:SC-70-5 封装:Reel |

| MAX921C/D DIE | 制造商:Maxim Integrated Products 功能描述: |

| MAX921C/D+ | 功能描述:校验器 IC RoHS:否 制造商:STMicroelectronics 产品: 比较器类型: 通道数量: 输出类型:Push-Pull 电源电压-最大:5.5 V 电源电压-最小:1.1 V 补偿电压(最大值):6 mV 电源电流(最大值):1350 nA 响应时间: 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:SC-70-5 封装:Reel |

| MAX921CPA | 功能描述:校验器 IC Single Comparator w/1% Precision Ref RoHS:否 制造商:STMicroelectronics 产品: 比较器类型: 通道数量: 输出类型:Push-Pull 电源电压-最大:5.5 V 电源电压-最小:1.1 V 补偿电压(最大值):6 mV 电源电流(最大值):1350 nA 响应时间: 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:SC-70-5 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。