- 您现在的位置:买卖IC网 > PDF目录11684 > MAX9250GCM+T (Maxim Integrated Products)IC DESERIALIZER LVDS 48-LQFP PDF资料下载

参数资料

| 型号: | MAX9250GCM+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 8/20页 |

| 文件大小: | 0K |

| 描述: | IC DESERIALIZER LVDS 48-LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,000 |

| 功能: | 解串器 |

| 数据速率: | 840Mbps |

| 输入类型: | LVDS |

| 输出类型: | LVCMOS |

| 输入数: | 1 |

| 输出数: | 27 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 带卷 (TR) |

MAX9248/MAX9250

27-Bit, 2.5MHz to 42MHz

DC-Balanced LVDS Deserializers

16

______________________________________________________________________________________

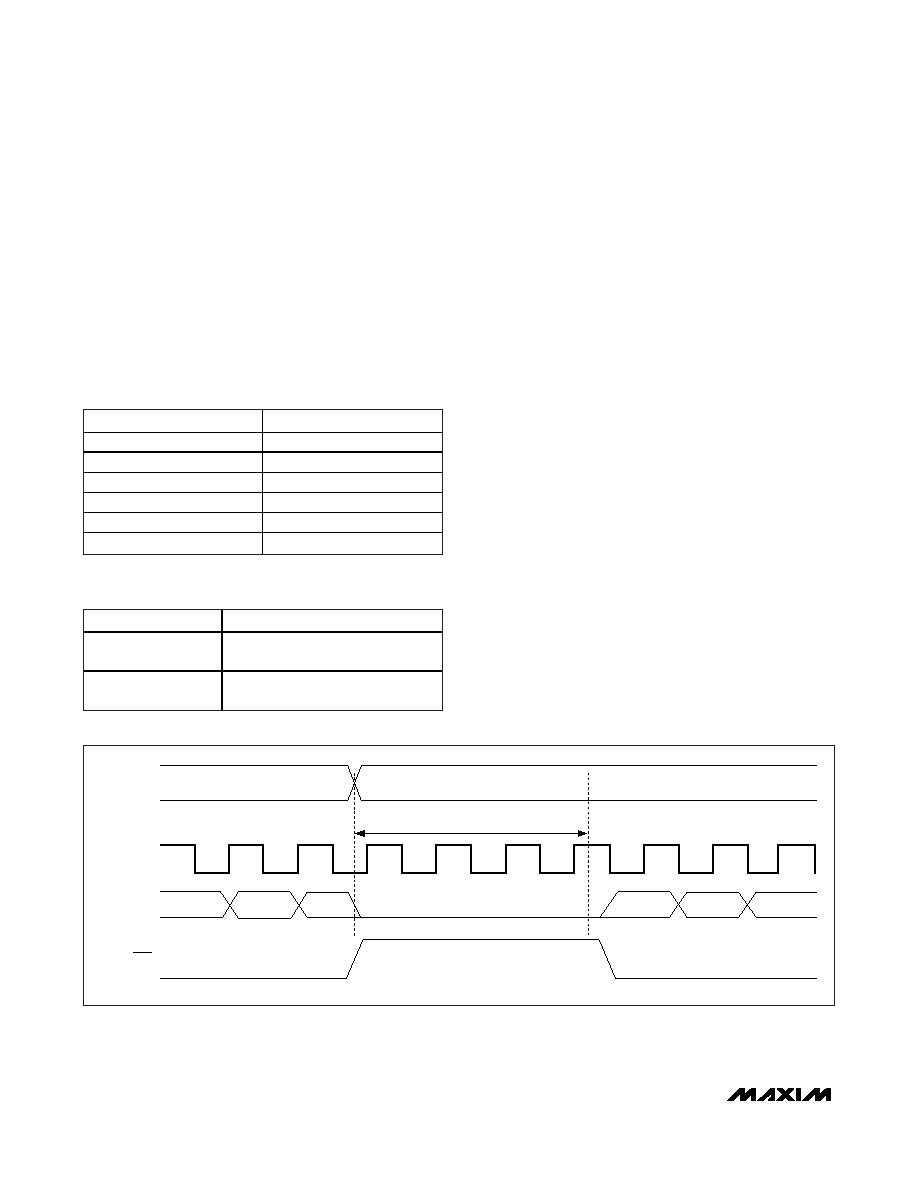

Spread-Spectrum Selection

The MAX9248 single-ended data and clock outputs are

programmable for a variation of ±2% or ±4% around

the LVDS input clock frequency. The modulation rate of

the frequency variation is 32kHz for a 33MHz LVDS

clock input and scales linearly with the clock frequency

(see Table 4). The output spread is controlled through

the SS input (see Table 5). Driving SS high spreads all

data and clock outputs by ±4%, while pulling low

spreads ±2%.

Any spread change causes a delay time of 32,000 x tT

before output data is valid. When the spread amount is

changed from ±2% to ±4% or vice versa, the data out-

puts go low for one tΔSSPLL delay (see Figure 17). The

data outputs stay low, but are not valid when the

spread amount is changed.

Output Enable (OUTEN) and

Busing Outputs

The outputs of two MAX9250s can be bused to form a

2:1 mux with the outputs controlled by the output

enable. Wait 30ns between disabling one deserializer

(driving OUTEN low) and enabling the second one (dri-

ving OUTEN high) to avoid contention of the bused out-

puts. OUTEN controls all outputs except LOCK.

Rising or Falling Output Latch Edge (R/F)

The MAX9248/MAX9250 have a selectable rising or

falling output latch edge through a logic setting on R/F.

Driving R/F high selects the rising output latch edge,

which latches the parallel output data into the next chip

on the rising edge of PCLK_OUT. Driving R/F low

selects the falling output latch edge, which latches the

parallel output data into the next chip on the falling

edge of PCLK_OUT. The MAX9248/MAX9250 output-

latch-edge polarity does not need to match the

MAX9247 serializer input-latch-edge polarity. Select the

latch-edge polarity required by the chip being driven

by the MAX9248/MAX9250.

tΔSSPLL (32,800 x tT)

±4% OR ±2% SPREAD

LOW

SS

PCLK_OUT

RGB_OUT[17:0]

CNTL_OUT8:0]

LOCK

Figure 17. Output Waveforms when Spread Amount is Changed

fPCLK_IN

fM(kHz) = fPCLK_IN / 1024

8

7.81

10

9.77

16

15.63

32

31.25

40

39.06

42

41.01

Table 4. Modulation Rate

SS INPUT LEVEL

OUTPUT SPREAD

High

Data and clock output spread ±4%

relative to REFCLK

Low

Data and clock output spread ±2%

relative to REFCLK

Table 5. SS Function

相关PDF资料 |

PDF描述 |

|---|---|

| MAX9247GCM+T | IC SERIALIZER LVDS 48-LQFP |

| D38999/24FG41SB | CONN RCPT 41POS JAM NUT W/SCKT |

| D38999/26FE99SA | CONN PLUG 23POS STRAIGHT W/SCKT |

| R5F100MLAFB#V0 | MCU 16BIT 512KB FLASH 80LQFP |

| D38999/26ME26HN | CONN PLUG 26POS STRAIGHT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9251 | 功能描述:串行器/解串器 - Serdes RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9252 | 功能描述:串行器/解串器 - Serdes RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9253 | 功能描述:串行器/解串器 - Serdes RoHS:否 制造商:Texas Instruments 类型:Deserializer 数据速率:1.485 Gbit/s 输入类型:ECL/LVDS 输出类型:LVCMOS 输入端数量:1 输出端数量:20 工作电源电压:2.375 V to 2.625 V 工作温度范围:0 C to + 70 C 封装 / 箱体:TQFP-64 |

| MAX9254 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:21-Bit Deserializers with Programmable Spread Spectrum and DC Balance |

| MAX9254EUM | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:21-Bit Deserializers with Programmable Spread Spectrum and DC Balance |

发布紧急采购,3分钟左右您将得到回复。