- 您现在的位置:买卖IC网 > PDF目录2089 > MAX9315EUP+T (Maxim Integrated Products)IC CLK/DATA BUFF MUX 2:5 20TSSOP PDF资料下载

参数资料

| 型号: | MAX9315EUP+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 8/11页 |

| 文件大小: | 0K |

| 描述: | IC CLK/DATA BUFF MUX 2:5 20TSSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 类型: | 扇出缓冲器(分配),多路复用器,数据 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:5 |

| 差分 - 输入:输出: | 是/是 |

| 输入: | HSTL,LVECL,LVPECL |

| 输出: | LVECL,LVPECL |

| 频率 - 最大: | 1.5GHz |

| 电源电压: | 2.25 V ~ 3.8 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 带卷 (TR) |

MAX9315

Detailed Description

The MAX9315 is a low-skew, 1-to-5 differential driver

designed for clock or data distribution. A 2-to-1 MUX

selects one of the two differential clock inputs, CLK0,

CLK0 or CLK1, CLK1. The MUX is switched by the sin-

gle-ended SEL input. A logic low selects the CLK0,

CLK0 input and a logic high selects the CLK1, CLK1

input. The SEL logic threshold is set by the internal volt-

age reference VBB. SEL can be driven to VCC and VEE

or by a single-ended LVPECL/LVECL signal. The

selected input is reproduced at five differential outputs.

Synchronous Enable

The MAX9315 is synchronously enabled and disabled

with outputs in the low state to eliminate shortened

clock pulses. EN is connected to the input of an edge-

triggered D flip-flop. After power-up, drive EN low and

toggle the selected clock input to enable the outputs.

The outputs are enabled on the falling edge of the

selected clock input after EN goes low. The outputs are

set to a low state on the falling edge of the selected

clock input after EN goes high. The threshold for EN is

equal to VBB.

Supply

For interfacing to differential HSTL and LVPECL signals,

the VCC range is from +2.375V to +3.8V (with VEE

grounded), allowing high-performance clock or data

distribution in systems with a nominal +2.5V or +3.3V

supply. For interfacing to differential LVECL, the VEE

range is -2.375V to -3.8V (with VCC grounded). Output

levels are referenced to VCC and are considered

LVPECL or LVECL, depending on the level of the VCC

supply. With VCC connected to a positive supply and

1:5 Differential LVPECL/LVECL/HSTL

Clock and Data Driver

6

_______________________________________________________________________________________

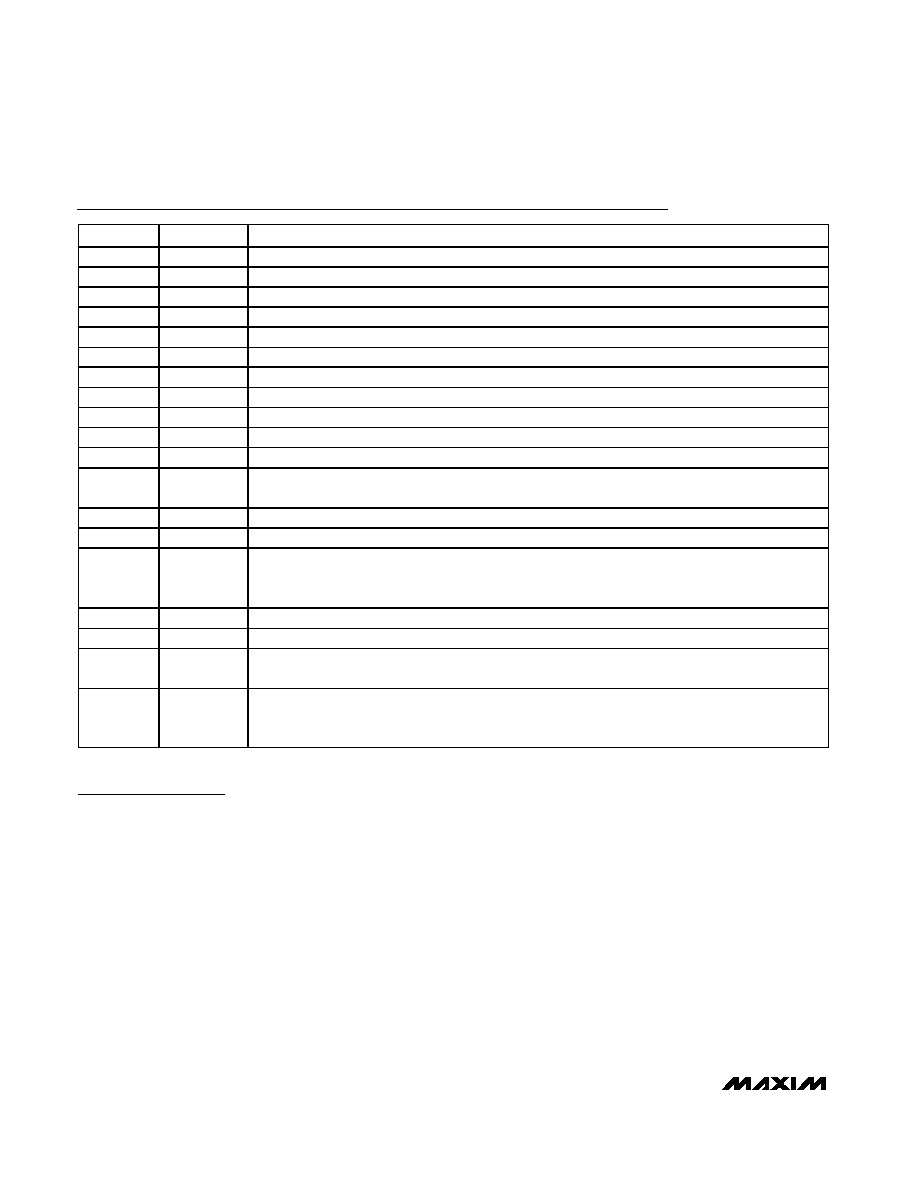

Pin Description

PIN

NAME

FUNCTION

1

Q0

Noninverting Q0 Output. Typically terminate with 50

resistor to VCC - 2V.

2

Q0

Inverting Q0 Output. Typically terminate with 50

resistor to VCC - 2V.

3

Q1

Noninverting Q1 Output. Typically terminate with 50

resistor to VCC - 2V.

4

Q1

Inverting Q1 Output. Typically terminate with 50

resistor to VCC - 2V.

5

Q2

Noninverting Q2 Output. Typically terminate with 50

resistor to VCC - 2V.

6

Q2

Inverting Q2 Output. Typically terminate with 50

resistor to VCC - 2V.

7

Q3

Noninverting Q3 Output. Typically terminate with 50

resistor to VCC - 2V.

8

Q3

Inverting Q3 Output. Typically terminate with 50

resistor to VCC - 2V.

9

Q4

Noninverting Q4 Output. Typically terminate with 50

resistor to VCC - 2V.

10

Q4

Inverting Q4 Output. Typically terminate with 50

resistor to VCC - 2V.

11

VEE

Negative Supply Voltage

12

SEL

Clock Select Input (Single Ended). Drive low to select the CLK0, CLK0 input. Drive high to select the

CLK1, CLK1 input. The SEL threshold is equal to VBB.

13

CLK0

Noninverting Differential Clock Input 0. Internal 75k

pulldown to VEE.

14

CLK0

Inverting Differential Clock Input 0. Internal 75k

pullup to VCC and 75k pulldown to VEE.

15

VBB

Reference Output Voltage. Connect to the inverting or noninverting clock input to provide a

reference for single-ended operation. When used, bypass with a 0.01F ceramic capacitor to VCC;

otherwise, leave open.

16

CLK1

Noninverting Differential Clock Input 1. Internal 75k

pulldown to VEE.

17

CLK1

Inverting Differential Clock Input 1. Internal 75k

pullup to VCC and 75k pulldown to VEE.

18, 20

VCC

Positive Supply Voltage. Bypass VCC to VEE with 0.1F and 0.01F ceramic capacitors. Place the

capacitors as close to the device as possible with the smaller value capacitor closest to the device.

19

EN

Output Enable Input. Outputs are synchronously enabled on the falling edge of the selected clock

input when EN is low. Outputs are synchronously driven low on the falling edge of the selected

clock input when EN is high.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX9316EWP+T | IC CLOCK BUFFER MUX 2:5 20-SOIC |

| MAX9320ESA+T | IC CLOCK BUFFER 2:2 3GHZ 8-SOIC |

| MAX9321EUA+T | IC CLOCK/DATA DRIVER 1:1 8-UMAX |

| MAX9325EQI+T | IC CLK/DATA BUFF MUX 2:8 28-PLCC |

| MAX934ESE+ | IC COMPARATOR W/REF 16-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX9315EUP-TG068 | 制造商:Maxim Integrated Products 功能描述:1:5 DIFFERENTIAL LVPECL/LVECL/HSTL CLOCK AND - Rail/Tube |

| MAX9315EVKIT | 功能描述:时钟驱动器及分配 Evaluation Kit for the MAX9315 MAX9316 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| MAX9316AEWP | 功能描述:时钟驱动器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| MAX9316AEWP-T | 功能描述:时钟驱动器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| MAX9316EUP | 制造商:Maxim Integrated Products 功能描述:1:5 DIFFERENTIAL LVPECL/LVECL/HSTL CLOCK AND - Rail/Tube |

发布紧急采购,3分钟左右您将得到回复。