- 您现在的位置:买卖IC网 > PDF目录80534 > MB91F346BPFT-GE1 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | MB91F346BPFT-GE1 |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, PQFP100 |

| 封装: | 12 X 12 MM, 1.20 MM HEIGHT, 0.40 MM PITCH, PLASTIC, TQFP-100 |

| 文件页数: | 12/72页 |

| 文件大小: | 657K |

| 代理商: | MB91F346BPFT-GE1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

MB91345 Series

2

On-chip multiplier supported at instruction level

Signed 32-bit multiplication : 5 cycles

Signed 16-bit multiplication : 3 cycles

Interrupt (PC, PS save) : 6 cycles, 16 priority levels

Harvard architecture allowing program access and data access to be executed simultaneously

Instruction set compatible with FR family

Internal memory

DMAC (DMA Controller)

5 channels

Two transfer factors (internal peripheral / software)

Addressing mode : 20/24-bit full-address selection (increment/decrement/fixed)

Transfer modes (burst transfer/step transfer/and block transfer)

Selectable transfer data sizes : 8, 16, or 32 bits

Bit search module (for REALOS)

Search for the position of the bit I/O-changed first in one word from the MSB

Reload timer : 3 channels (including 1channel for REALOS)

16-bit timer

The internal clock is optional from 2/8/32 division

Multi function serial interface

11 channels

Full duplex double buffer

2 channels out of 11 channels with 16-byte FIFO

Capable of selecting communication mode : asynchronous (Start-Stop synchronous) communication, clock

synchronous communication (Max 8.25 Mbps) , I2C* standard mode (Max 100 kbps) , high-speed mode (Max

400 kbps)

Parity on/off selectable

Baud rate generator per channel

Abundant error detection functions are provided (Parity, frame, and overrun)

External clock can be used as transfer clock

ch.0, ch.1, ch.2, and ch.10 is tolerant of 5 V

Interrupt controller

A total of 24 external interrupt lines (external interrupt pins INT23 to INT0)

Interrupt from internal peripheral

Programmable 16 priority levels

Available for wakeup from STOP mode

(Continued)

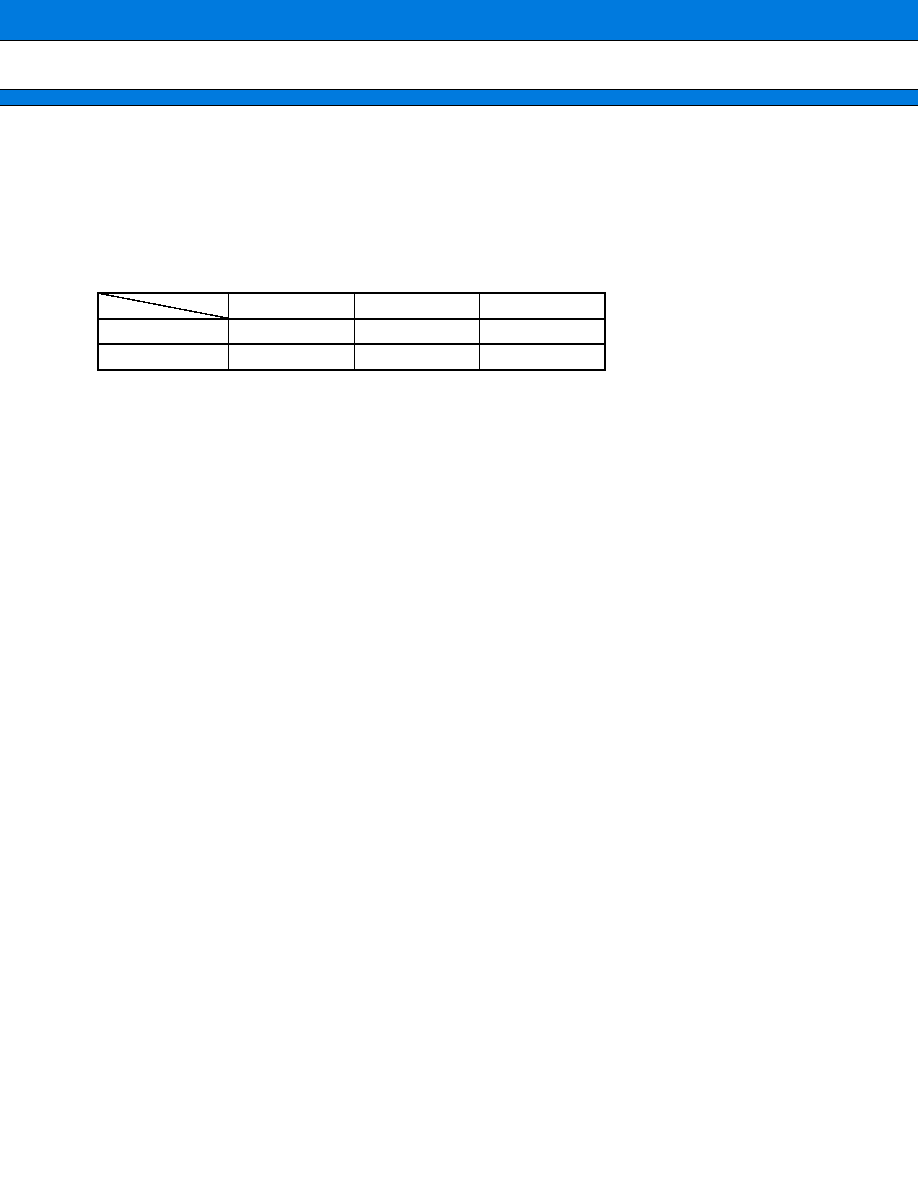

Flash

D-bus RAM

F-bus RAM

MB91F345B

512 Kbytes

24 Kbytes

8 Kbytes

MB91F346B

1 Mbyte

24 Kbytes

8 Kbytes

相关PDF资料 |

PDF描述 |

|---|---|

| MSM80C31F-1GS-VIK | 8-BIT, 16 MHz, MICROCONTROLLER, PQFP44 |

| MAQ281CB | 16-BIT, MICROPROCESSOR, DMA64 |

| MAR281CC | 16-BIT, MICROPROCESSOR, DMA64 |

| MD80C51UFXXX-25 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CDIP40 |

| MD80C51UXXX-25 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CDIP40 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MB91F353A | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:32-bit Microcontroller |

| MB91F353APMCR-GE1 | 制造商:FUJITSU 功能描述: |

| MB91F353APMCR-G-JNE1 | 制造商:FUJITSU 功能描述: |

| MB91F353APMT | 制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:32-bit Microcontroller |

| MB91F353APMT-GE1 | 制造商:FUJITSU 功能描述:IC 16BIT MCU 5V SMD LQFP120 |

发布紧急采购,3分钟左右您将得到回复。