- 您现在的位置:买卖IC网 > PDF目录45211 > MC68332GVFV20 (FREESCALE SEMICONDUCTOR INC) 32-BIT, 20 MHz, MICROCONTROLLER, PQFP144 PDF资料下载

参数资料

| 型号: | MC68332GVFV20 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 20 MHz, MICROCONTROLLER, PQFP144 |

| 封装: | 20 X 20 MM, 1.40 MM HEIGHT, 0.50 MM PITCH, LQFP-144 |

| 文件页数: | 31/109页 |

| 文件大小: | 787K |

| 代理商: | MC68332GVFV20 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页

MOTOROLA

MC68332

28

MC68332TS/D

3.4.8 Data Transfer Mechanism

The MCU architecture supports byte, word, and long-word operands, allowing access to 8- and 16-bit

data ports through the use of asynchronous cycles controlled by the data transfer and size acknowledge

inputs (DSACK1 and DSACK0).

3.4.9 Dynamic Bus Sizing

The MCU dynamically interprets the port size of the addressed device during each bus cycle, allowing

operand transfers to or from 8- and 16-bit ports. During an operand transfer cycle, the slave device sig-

nals its port size and indicates completion of the bus cycle to the MCU through the use of the DSACK0

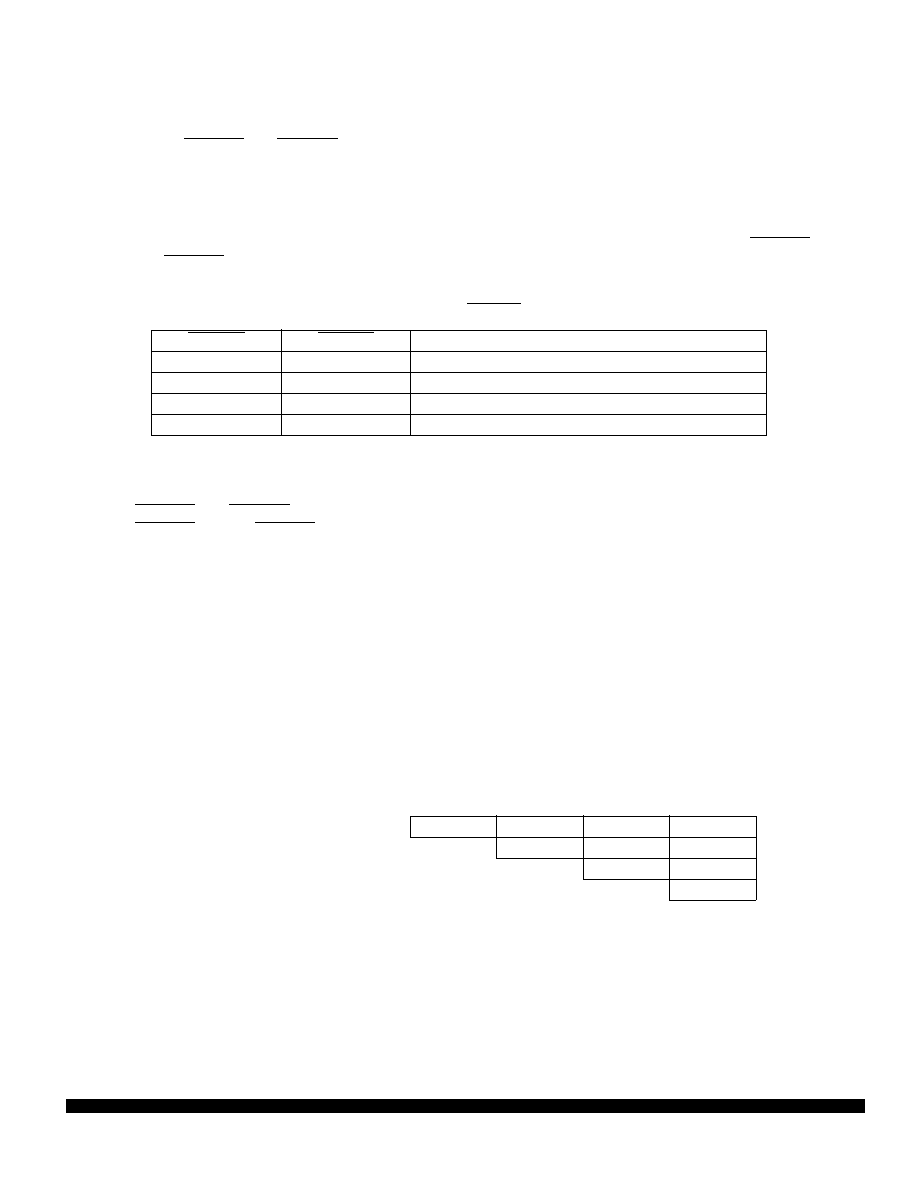

and DSACK1 inputs, as shown in the following table.

For example, if the MCU is executing an instruction that reads a long-word operand from a 16-bit port,

the MCU latches the 16 bits of valid data and then runs another bus cycle to obtain the other 16 bits.

The operation for an 8-bit port is similar, but requires four read cycles. The addressed device uses the

DSACK0 and DSACK1 signals to indicate the port width. For instance, a 16-bit device always returns

DSACK0 = 1 and DSACK1 = 0 for a 16-bit port, regardless of whether the bus cycle is a byte or word

operation.

Dynamic bus sizing requires that the portion of the data bus used for a transfer to or from a particular

port size be fixed. A 16-bit port must reside on data bus bits [15:0] and an 8-bit port must reside on data

bus bits [15:8]. This minimizes the number of bus cycles needed to transfer data and ensures that the

MCU transfers valid data.

The MCU always attempts to transfer the maximum amount of data on all bus cycles. For a word oper-

ation, it is assumed that the port is 16 bits wide when the bus cycle begins. Operand bytes are desig-

nated as shown in the following figure. OP0 is the most significant byte of a long-word operand, and

OP3 is the least significant byte. The two bytes of a word-length operand are OP0 (most significant) and

OP1. The single byte of a byte-length operand is OP0.

Figure 8 Operand Byte Order

3.4.10 Operand Alignment

The data multiplexer establishes the necessary connections for different combinations of address and

data sizes. The multiplexer takes the two bytes of the 16-bit bus and routes them to their required po-

sitions. Positioning of bytes is determined by the size and address outputs. SIZ1 and SIZ0 indicate the

remaining number of bytes to be transferred during the current bus cycle. The number of bytes trans-

ferred is equal to or less than the size indicated by SIZ1 and SIZ0, depending on port width.

Table 10 Effect of DSACK Signals

DSACK1

DSACK0

Result

1

Insert Wait States in Current Bus Cycle

1

0

Complete Cycle —Data Bus Port Size is 8 Bits

0

1

Complete Cycle —Data Bus Port Size is 16 Bits

0

Reserved

Operand

Byte Order

31

24

23

16

15

8

7

0

Long Word

OP0

OP1

OP2

OP3

Three Byte

OP0

OP1

OP2

Word

OP0

OP1

Byte

OP0

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

..

.

相关PDF资料 |

PDF描述 |

|---|---|

| MC68332GCAG25 | 32-BIT, 25 MHz, MICROCONTROLLER, PQFP144 |

| MC68332GMFC16 | 32-BIT, 16 MHz, MICROCONTROLLER, PQFP132 |

| MC68332MFV20 | 32-BIT, 20 MHz, MICROCONTROLLER, PQFP144 |

| MC68332ACPV25 | 32-BIT, 25 MHz, MICROCONTROLLER, PQFP144 |

| MC68332GCPV25 | 32-BIT, 25 MHz, MICROCONTROLLER, PQFP144 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC68332GVPV16 | 制造商:Rochester Electronics LLC 功能描述:32BIT MCU,2KRAM,TPU,QSM - Bulk |

| MC68332MFC16 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:32-Bit Modular Microcontroller |

| MC68332MFC20 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:32-Bit Modular Microcontroller |

| MC68332MFV16 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:32-Bit Modular Microcontroller |

| MC68332MFV20 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:32-Bit Modular Microcontroller |

发布紧急采购,3分钟左右您将得到回复。