- 您现在的位置:买卖IC网 > PDF目录69028 > MC68HC16S2CPU25 (FREESCALE SEMICONDUCTOR INC) 16-BIT, 25.17 MHz, MICROCONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | MC68HC16S2CPU25 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, 25.17 MHz, MICROCONTROLLER, PQFP100 |

| 封装: | TQFP-100 |

| 文件页数: | 40/104页 |

| 文件大小: | 812K |

| 代理商: | MC68HC16S2CPU25 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

MOTOROLA

MC68HC16S2

40

MC68HC16S2TS/D

Data lines have weak internal pull-up drivers. External bus loading can overcome the weak internal pull-

up drivers on data bus lines, and hold pins low during reset. Use an active device to hold data bus lines

low. Data bus configuration logic must release the bus before the first bus cycle after reset to prevent

conflict with external memory devices. The first bus cycle occurs ten CLKOUT cycles after RESET is

released. If external mode selection logic causes a conflict of this type, an isolation resistor on the driven

lines may be required.

3.8.2 Functions of Pins for Other Modules During Reset

Generally, pins associated with modules other than the SIM default to port functions, and input/output

ports are set to input state. This is accomplished by disabling pin functions in the appropriate control

registers, and by clearing the appropriate port data direction registers. Refer to individual module sec-

tions in this manual for more information. Table 32 is a summary of module pin function out of reset.

3.8.3 Reset Timing

The RESET input must be asserted for a specified minimum period in order for reset to occur. External

RESET assertion can be delayed internally for a period equal to the longest bus cycle time (or the bus

monitor timeout period) in order to protect write cycles from being aborted by reset. While RESET is

asserted, SIM pins are either in a disabled high-impedance state or are driven to their inactive states.

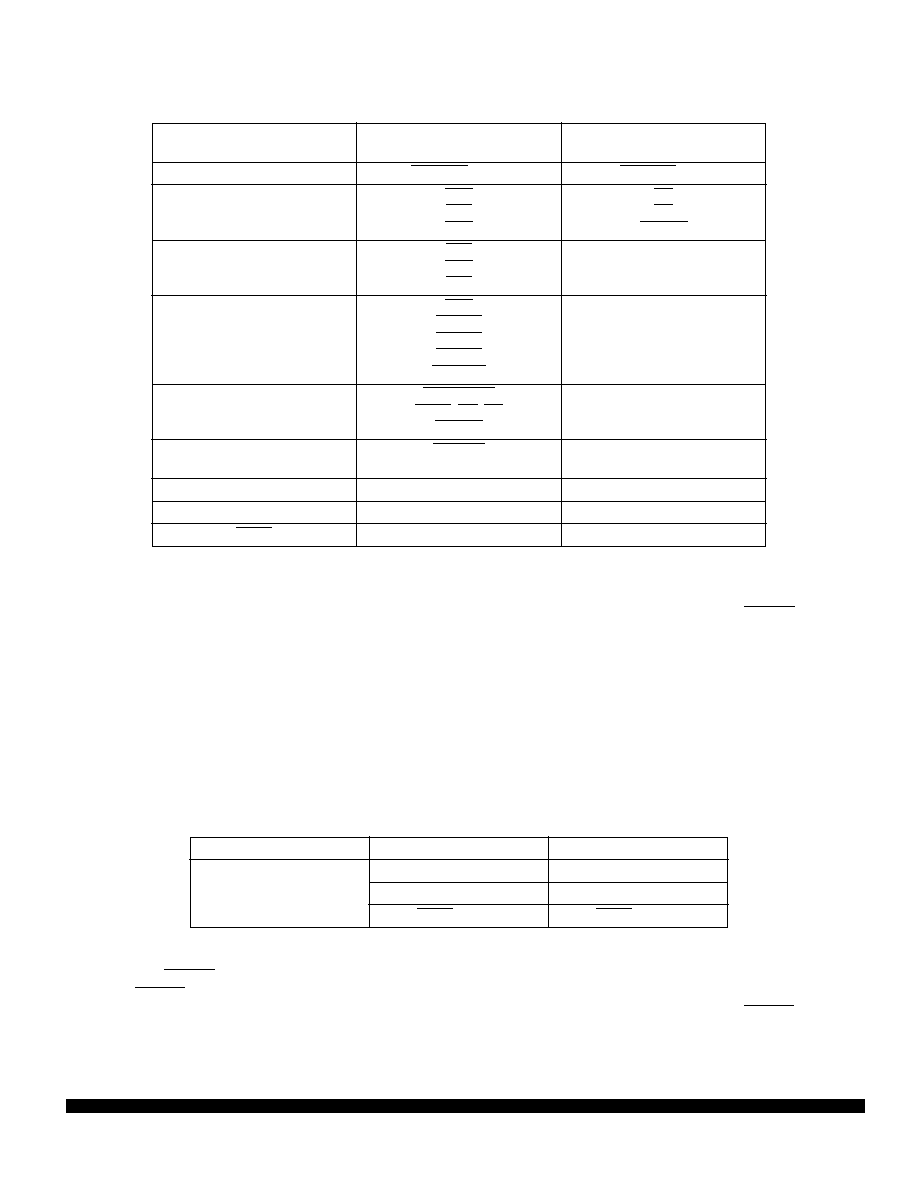

Table 31 Reset Mode Selection

Mode Select Pin

Default Function

(Pin Left High)

Alternate Function

(Pin Pulled Low)

DATA0

CSBOOT 16-Bit

CSBOOT 8-Bit

DATA1

CS0

CS1

CS2

BR

BG

BGACK

DATA2

CS3

CS4

CS5

FC0

FC1

FC2

DATA3

DATA4

DATA5

DATA6

DATA7

CS6

CS[7:6]

CS[8:6]

CS[9:6]

CS[10:6]

ADDR19

ADDR[20:19]

ADDR[21:19]

ADDR[22:19]

ADDR[23:19]

DATA8

DSACK[1:0]

AVEC, DS, AS

SIZ[1:0]

PORTE

DATA9

IRQ[7:1]

MODCLK

PORTF

DATA11

Test mode disabled

Test mode enabled

MODCLK

VCO = System clock

EXTAL = System clock

BKPT

Background mode disabled

Background mode enabled

Table 32 Module Pin Functions

Module

Pin Mnemonic

Function

CPU16

DSI/IPIPE1

DSO/IPIPE0

BKPT/DSCLK

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

..

.

相关PDF资料 |

PDF描述 |

|---|---|

| MC16S2CPU20B1 | 16-BIT, 20.97 MHz, MICROCONTROLLER, PQFP100 |

| MC68HC16X1CTH | 16-BIT, MROM, 16.78 MHz, MICROCONTROLLER, PQFP120 |

| MC68HC24VP | 16 I/O, PIA-GENERAL PURPOSE, PDIP40 |

| MC68HC33CFG | 48 I/O, PIA-GENERAL PURPOSE, PQFP100 |

| MC68HC33FG | 48 I/O, PIA-GENERAL PURPOSE, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC68HC16Z1CAG | 制造商:Freescale Semiconductor 功能描述: |

| MC68HC16Z1CAG16 | 功能描述:16位微控制器 - MCU 16 BIT MCU 1K RAM RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT |

| MC68HC16Z1CAG16 | 制造商:Freescale Semiconductor 功能描述:IC16-BIT MICROCONTROLLER |

| MC68HC16Z1CAG20 | 功能描述:16位微控制器 - MCU 16 BIT MCU 1K RAM RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT |

| MC68HC16Z1CAG20 | 制造商:Freescale Semiconductor 功能描述:Microcontroller |

发布紧急采购,3分钟左右您将得到回复。