- 您现在的位置:买卖IC网 > PDF目录371089 > MCM64E918 (Motorola, Inc.) 8M Bit synchronous late write fast static RAM(8M位同步迟写快速静态RAM) PDF资料下载

参数资料

| 型号: | MCM64E918 |

| 厂商: | Motorola, Inc. |

| 英文描述: | 8M Bit synchronous late write fast static RAM(8M位同步迟写快速静态RAM) |

| 中文描述: | 晚8分位同步静态随机存储器写入速度(800万位同步迟写快速静态内存) |

| 文件页数: | 16/24页 |

| 文件大小: | 503K |

| 代理商: | MCM64E918 |

MCM64E918

MCM64E836

16

MOTOROLA FAST SRAM

SERIAL BOUNDARY SCAN TEST ACCESS PORT OPERATION

OVERVIEW

The serial boundary scan test access port (TAP) on this

RAM is designed to operate in a manner consistent with

IEEE Standard 1149.1–1990 (commonly referred to as

JTAG), but does not implement all of the functions required

for IEEE 1149.1 compliance. Certain functions have been

modified or eliminated because their implementation places

extra delays in the RAMs critical speed path. Nevertheless,

the RAM supports the standard TAP controller architecture

(the TAP controller is the state machine that controls the

TAPs operation) and can be expected to function in a manner

that does not conflict with the operation of devices with IEEE

1149.1 compliant TAPs. The TAP operates using conven-

tional JEDEC Standard 8–5 (2.5 V) logic level signaling.

DISABLING THE TEST ACCESS PORT

It is possible to use this device without utilizing the TAP. To

disable the TAP controller without interfering with normal

operation of the device, TCK must be tied to VSS to preclude

mid–level inputs. TDI and TMS are designed so an undriven

input will produce a response identical to the application of a

logic 1, and may be left unconnected. But they may also be

tied to VDD through a 1 k resistor. TDO should be left uncon-

nected.

TAP DC OPERATING CHARACTERISTICS

(2.375 V

≤

VDD

≤

2.625 V, 0

°

C

≤

TA

≤

70

°

C, Unless Otherwise Noted)

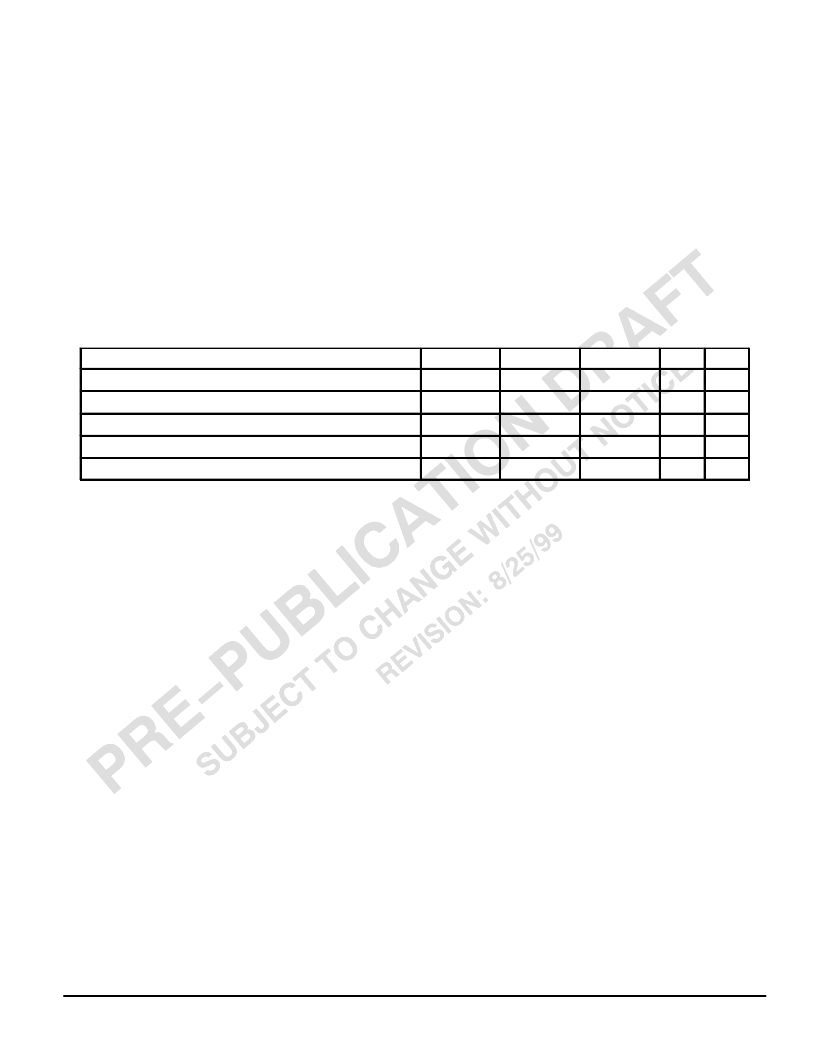

Parameter

Symbol

Min

Max

Unit

Notes

Logic Input Logic High

VIH1

1.2

VDD + 0.3

V

Logic Input Logic Low

VIL1

– 0.3

0.4

V

Logic Input Leakage Current

Ilkg

—

±

5

μ

A

1

CMOS Output Logic Low

VOL1

—

0.2

V

2

CMOS Output Logic High

VOH1

VDDQ – 0.2

—

V

3

NOTES:

1. 0 V

≤

Vin

≤

VDD for all logic input pins.

2. IOL1

≤

100

μ

A @ VOL = 0.2 V. Sampled, not 100% tested.

3.

IOH1

≤

100

μ

A @ VDDQ – 0.2 V. Sampled, not 100% tested.

相关PDF资料 |

PDF描述 |

|---|---|

| MCM64PC32TSG66 | 256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| MCM64PC64TSG66 | 256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| MCM64PC32T | 256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| MCM6706RJ8 | 32K x 8 Bit Static Random Access Memory |

| MCM6706J6 | Circular Connector; Body Material:Aluminum; Series:PT06; Number of Contacts:41; Connector Shell Size:20; Connecting Termination:Crimp; Circular Shell Style:Straight Plug; Circular Contact Gender:Socket; Insert Arrangement:20-41 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MCM64PC32 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| MCM64PC32SG66 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| MCM64PC32T | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| MCM64PC32TSG66 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| MCM64PC64SG66 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

发布紧急采购,3分钟左右您将得到回复。