- 您现在的位置:买卖IC网 > PDF目录1853 > MCZ34702EWR2 (Freescale Semiconductor)IC PWR SUPPLY 3A SW 32-SOIC PDF资料下载

参数资料

| 型号: | MCZ34702EWR2 |

| 厂商: | Freescale Semiconductor |

| 文件页数: | 13/39页 |

| 文件大小: | 0K |

| 描述: | IC PWR SUPPLY 3A SW 32-SOIC |

| 标准包装: | 1,000 |

| 应用: | 控制器,电源 QUICC? I、II |

| 输入电压: | 2.8 V ~ 6 V |

| 输出数: | 2 |

| 输出电压: | 7.75V,0.8 V ~ 6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 32-SOIC |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页

�� �

�

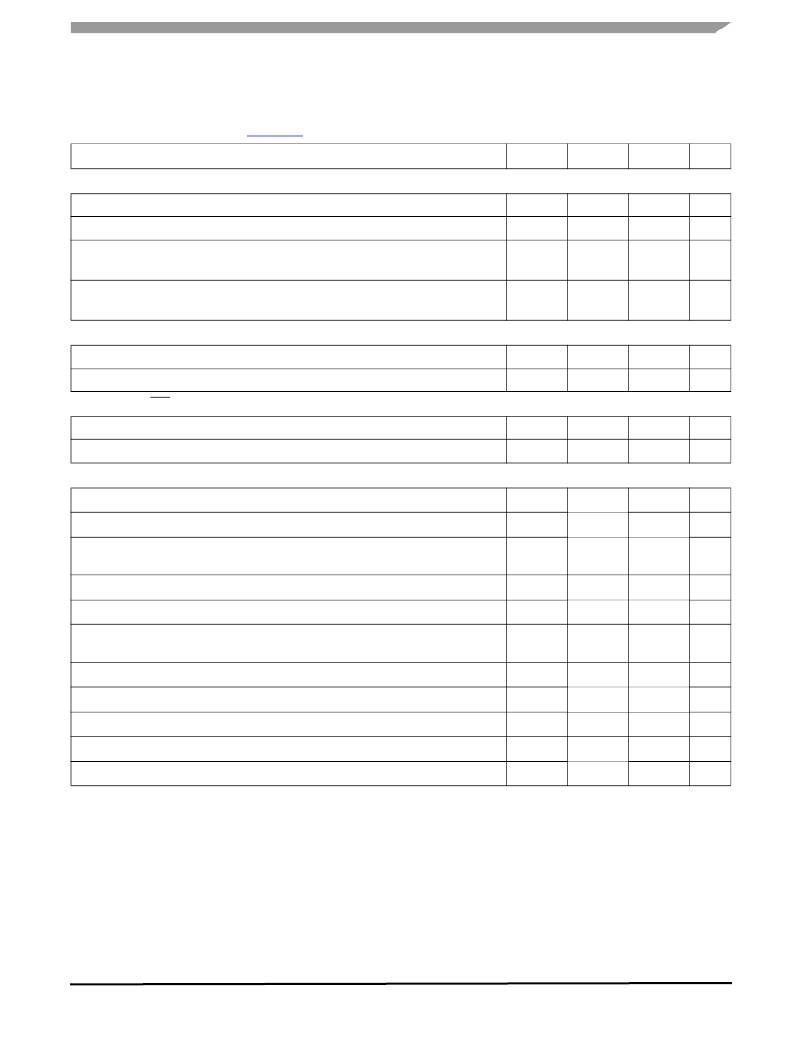

ELECTRICAL� CHARACTERISTICS�

�DYNAMIC� ELECTRICAL� CHARACTERISTICS�

�Table� 4.� DYNAMIC� ELECTRICAL� CHARACTERISTICS� (continued)�

�Characteristics� noted� under� conditions� -40°C� ?� T� A� ?� 85� ?� C� unless� otherwise� noted.� Input� voltages� VIN1� =� VIN2� =� 3.3V� using�

�the� typical� application� circuit� (see� Figures� 33� ),� unless� otherwise� noted.�

�Characteristic�

�Symbol�

�Min�

�Typ�

�Max�

�Unit�

�BOOST� REGULATOR�

�Boost� Regulator� MOSFET� Maximum� ON� Time� (21)�

�Boost� Regulator� Control� Loop� Propagation� Delay� (21)�

�(21)�

�Boost� Switching� Node� VBD� Rise� Time�

�t� ON�

�t� BST_PD�

�t� B_RISE�

�–�

�–�

�24�

�50�

�–�

�–�

�?� s�

�ns�

�ns�

�IBST� =� 20mA�

�Boost� Switching� Node� VBD� Fall� Time� (21)�

�IBST� =� 20mA�

�LINEAR� REGULATOR� (LDO)�

�t� B_FALL�

�–�

�–�

�5.0�

�3.0�

�ns�

�Fault� Condition� Time-Out�

�Retry� Timer� Cycle�

�t� FAULT�

�t� RET�

�8.0�

�80�

�10�

�100�

�12�

�120�

�ms�

�ms�

�Reset� Monitor� (� RST� )�

�Monitoring� LFB� Pin� Delay�

�Monitoring� INV� Pin� Delay�

�t� D_RST_LFB�

�t� D_RST_INV�

�12�

�12�

�–�

�–�

�28�

�28�

�?� s�

�?� s�

�SCA,� SCL� PIN,� I� 2� C� BUS� (STANDARD)�

�SCL� Clock� Frequency� (21)�

�Bus� Free� Time� Between� a� STOP� and� a� START� Condition� (21)�

�Hold� Time� (Repeated)� START� Condition� (After� this� period,� the� first� clock�

�pulse� is� generated)� (21)�

�Low� Period� of� the� SCL� Clock� (21)�

�High� Period� of� the� SCL� Clock� (21)�

�SDA� Fall� Time� from� VIH_MAX� to� VIL_MIN,� Bus� Capacitance� 10pF� to� 400pF,�

�3.0mA� Sink� Current� (21)� ,� (23)�

�Setup� Time� for� a� Repeated� START� Condition� (21)�

�Data� Hold� Time� for� I� 2� C� Bus� Devices� (21)� ,� (22)�

�Data� Setup� Time� (21)�

�Setup� Time� for� STOP� Condition� (21)�

�Capacitive� Load� for� Each� Bus� Line� (21)�

�f� SCL�

�t� BUF�

�t� HD-STA�

�t� LOW�

�t� HIGH�

�t� F�

�t� SU-STA�

�t� HD-DAT�

�t� SU-DA� T�

�t� SU-STO�

�CB�

�–�

�4.7�

�4.0�

�4.7�

�4.0�

�–�

�4.7�

�0.0�

�250�

�4.0�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�100�

�–�

�–�

�–�

�–�

�250�

�–�

�–�

�–�

�–�

�400�

�kHz�

�?� s�

�?� s�

�?� s�

�?� s�

�ns�

�?� s�

�?� s�

�ns�

�?� s�

�pF�

�Notes�

�21.� Design� information� only.� This� parameter� is� not� production� tested.�

�22.� The� device� provides� an� internal� hold� time� of� at� least� 300ns� for� the� SDA� signal� (refer� to� the� V� IH_MIN� of� the� SCL� signal)� to� bridge� the�

�undefined� region� of� the� falling� edge� of� SCL.�

�23.� VIH� =� High� level� voltage� on� I2C� bus� and� VIL� =� Low� level� voltage� on� I2C� bus�

�34702�

�Analog� Integrated� Circuit� Device� Data� ?�

�Freescale� Semiconductor�

�13�

�相关PDF资料 |

PDF描述 |

|---|---|

| MDC3105DMT1 | IC INDUCTVE LOAD DRIVR 8V SC74-6 |

| MDP-02 | PLUG DBL BANANA W/WIRE GUIDE SET |

| MDP-S-9 | PLUG DBL BANANA W/SHORT BAR WHT |

| MDP-ST | PLUG DBL BANANA W/SOLDER TURRET |

| MDP-X | PLUG DBL BANANA ISOLAT W/4 TERM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MCZ36304201 | 制造商:LG Corporation 功能描述:Duct |

| MCZ36305001 | 制造商:LG Corporation 功能描述:Duct |

| MCZ36444401 | 制造商:LG Corporation 功能描述:Duct |

| MCZ36620901 | 制造商:LG Corporation 功能描述:Duct |

| MCZ37250851 | 制造商:LG Corporation 功能描述:Duct |

发布紧急采购,3分钟左右您将得到回复。