- 您现在的位置:买卖IC网 > PDF目录2013 > MK1575-01GILF (IDT, Integrated Device Technology Inc)IC CLK RECOVERY PLL 16-TSSOP PDF资料下载

参数资料

| 型号: | MK1575-01GILF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 7/14页 |

| 文件大小: | 0K |

| 描述: | IC CLK RECOVERY PLL 16-TSSOP |

| 标准包装: | 96 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 是 |

| 主要目的: | 视频 |

| 输入: | 时钟 |

| 输出: | LVCMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:2 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 80MHz |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 16-TSSOP |

| 包装: | 管件 |

| 其它名称: | 800-2630-5 MK1575-01GILF-ND |

MK1575-01

CLOCK RECOVERY PLL

CLOCK SYNTHESIZER

IDT CLOCK RECOVERY PLL

2

MK1575-01

REV P 051310

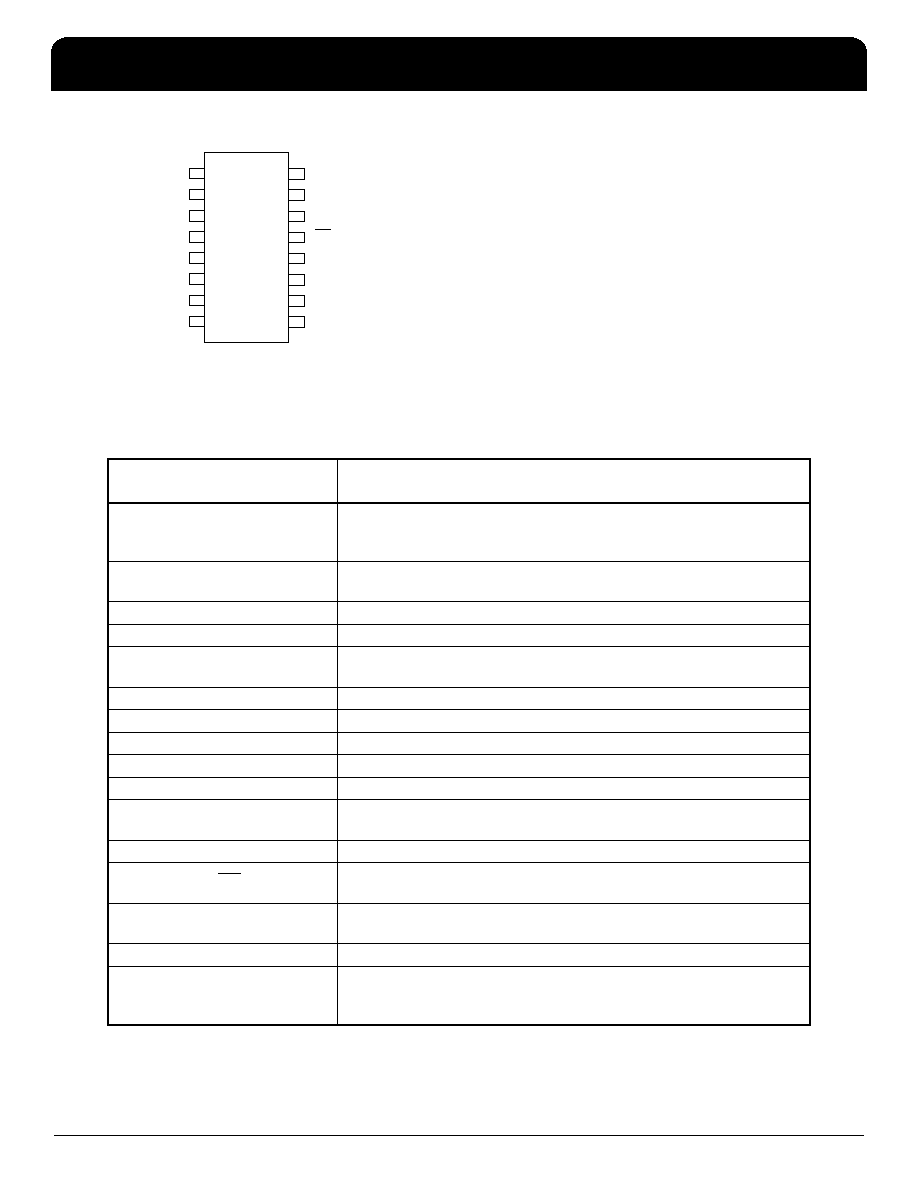

Pin Assignment

16 pin 4.40 mil body, 0.65 mil pitch TSSOP

Pin Descriptions

12

1

11

2

10

REFIN

FBIN

3

9

FS0

4

VDDA

NC

5

VDDD

6

FCLK

7

FS1

8

GNDA

OE

CLK2

FS2

GNDD

CLK1

CHGP

CHPR

16

15

14

13

Pin

Number

Pin

Name

Pin

Type

Pin Description

1

REFIN

Input

Reference clock input. Connect the input clock to this pin. Can be

Rising or Falling edge triggered as per Detailed Mode Selection Table,

page 3.

2FS0

Input

Frequency Selection Input bit 0, selects internal divider values as per

Detailed Mode Selection Table, page 3.

3

VDDA

Power

Power supply connection for internal VCO and other analog circuits.

4

VDDD

Power

Power supply connection for internal digital circuits and output buffers.

5FS1

Input

Frequency Selection Input bit 1, selects internal divider values as per

Detailed Mode Selection Table, page 3.

6

GNDA

Ground

Ground connection for internal VCO and other analog circuits.

7

GNDD

Ground

Ground connection for internal digital circuits and output buffers.

8

CHGP

—

Loop filter connection, active node.

9

CHPR

—

Loop filter connection, reference node. Do not connect to ground.

10

CLK1

Output

Output clock 1.

11

FS2

Input

Frequency Selection Input bit 2, selects internal divider values as per

Detailed Mode Selection Table, page 3.

12

CLK2

Output

Output clock 2.

13

OE

Input

Output Enable, tristates CLK1, CLK2, FCLK and powers down PLL

when high. Internal pull-up.

14

FCLK

Output

Feedback clock output, connect to FBIN for the pre-configured

frequency combinations listed in the tables on page 1.

15

NC

—

No internal connection, connect to ground.

16

FBIN

Input

Feedback clock input. Connect to CLK1, CLK2, FCLK, or the output of

an external feedback divider, depending on application. Refer to

document text for more information.

相关PDF资料 |

PDF描述 |

|---|---|

| MK1704ALF | IC CLK GENERATOR LOW EMI 8-SOIC |

| MK1705ALF | IC CLK GEN ATI LOW EMI 8-SOIC |

| MK1707SLF | IC CLK GENERATOR LOW EMI 8-SOIC |

| MK1714-01RILF | IC CLK MULT SPRD SPECTRUM 20QSOP |

| MK1716-01RTR | IC CLK SOURCE SER PROGR 28-QSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK1575-01GILFTR | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK1575-01GITR | 功能描述:IC CLK RECOVERY PLL 16-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| MK1575-01GLF | 功能描述:时钟发生器及支持产品 CLOCK RECOVERY PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK1575-01GLFTR | 功能描述:时钟发生器及支持产品 CLOCK RECOVERY PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK1575-01GTR | 功能描述:IC CLK RECOVERY PLL 16-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。