- 您现在的位置:买卖IC网 > PDF目录95954 > MK2049-34SITR (INTEGRATED DEVICE TECHNOLOGY INC) 77.76 MHz, OTHER CLOCK GENERATOR, PDSO20 PDF资料下载

参数资料

| 型号: | MK2049-34SITR |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 77.76 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| 封装: | 0.300 INCH, SOIC-20 |

| 文件页数: | 1/9页 |

| 文件大小: | 96K |

| 代理商: | MK2049-34SITR |

DATASHEET

3.3 VOLT COMMUNICATIONS CLOCK VCXO PLL

MK2049-34

IDT 3.3 VOLT COMMUNICATIONS CLOCK VCXO PLL

1

MK2049-34

REV F 102203

Description

The MK2049-34 is a VCXO Phased Locked Loop (PLL)

based clock synthesizer that accepts multiple input

frequencies. With an 8 kHz clock input as a reference, the

MK2049-34 generates T1, E1, T3, E3, ISDN, xDSL, and

other communications frequencies. This allows for the

generation of clocks frequency-locked and phase-locked to

an 8 kHz backplane clock, simplifying clock synchronization

in communications systems. The MK2409-34 can also

accept a T1 or E1 input clock and provide the same output

for loop timing. All outputs are frequency locked together

and to the input.

This part also has a jitter-attenuated Buffer capability. In this

mode, the MK2049-34 is ideal for filtering jitter from 27 MHz

video clocks or other clocks with high jitter.

ICS can customize these devices for many other different

frequencies.

Features

Packaged in 20-pin SOIC

3.3 V + 5% operation

Fixed I/O phase relationship on all selections

Meets the TR62411, ETS300 011, and GR-1244

specification for MTIE, Pull-in/Hold-in Range, Phase

Transients, and Jitter Generation for Stratum 3, 4, and 4E

Accepts multiple inputs: 8 kHz backplane clock, Loop

Timing frequencies, or 10 to 36 MHz

Locks to 8 kHz + 100 ppm (External mode)

Buffer Mode allows jitter attenuation of 10 to 36 MHz

input and x1/x0.5 or x2/x4 outputs

Exact internal ratios enable zero ppm error

Output clock rates include T1, E1, T3, E3, ISDN, xDSL,

and the OC3 submultiples

See also the MK2049-36 and MK2049-45

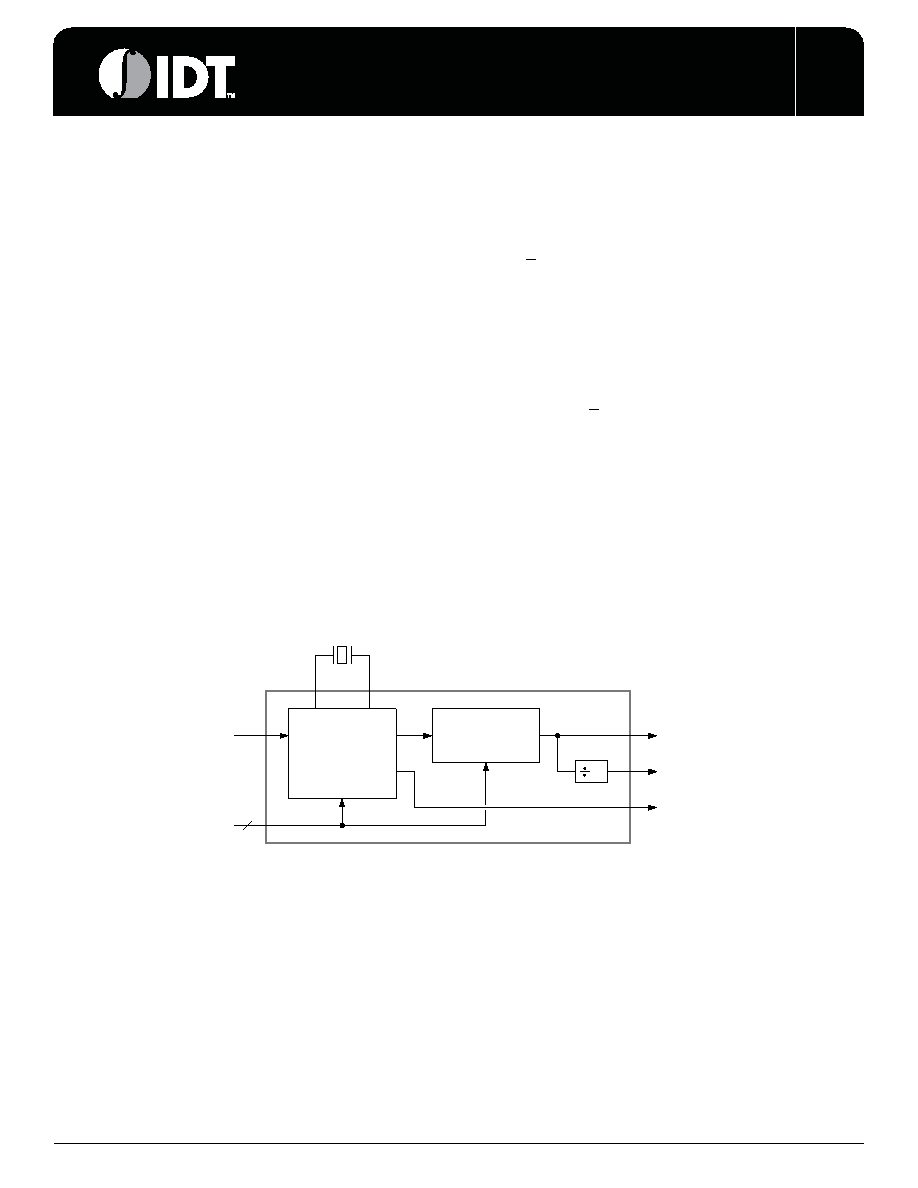

Block Diagram

VCXO-BASED

PLL

(MASTER CLOCK

GENERATOR)

EXTERNAL PULLABLE CRYSTAL

(external loop filter)

FREQUENCY

MULTIPLYING

PLL

2

INPUT REFERENCE

CLOCK

(TYPICALLY 8KHZ)

CLOCK OUTPUT

CLOCK OUTPUT / 2

8 KHZ (REGENERATED)

4

FREQUENCY SELECT

相关PDF资料 |

PDF描述 |

|---|---|

| MK2704S | 36.864 MHz, VIDEO CLOCK GENERATOR, PDSO8 |

| MK2705S | 24.576 MHz, VIDEO CLOCK GENERATOR, PDSO8 |

| MK2716S | 74.25 MHz, VIDEO CLOCK GENERATOR, PDSO8 |

| MK2727SLF | 27 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| MK2732-06GLF | 54 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK2049-35 | 制造商:ICS 制造商全称:ICS 功能描述:3.3 V Communications Clock PLL |

| MK2049-35SI | 制造商:Integrated Device Technology Inc 功能描述:49.152 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-35SITR | 制造商:ICS 制造商全称:ICS 功能描述:3.3 V Communications Clock PLL |

| MK2049-36 | 制造商:ICS 制造商全称:ICS 功能描述:3.3 V Communications Clock PLL |

| MK2049-36SI | 功能描述:IC VCXO PLL CLK SYNTH 20-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。