- 您现在的位置:买卖IC网 > PDF目录65811 > MK2049-44SILF 51.84 MHz, OTHER CLOCK GENERATOR, PDSO20 PDF资料下载

参数资料

| 型号: | MK2049-44SILF |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 51.84 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| 封装: | 0.300 INCH, SOIC-20 |

| 文件页数: | 5/9页 |

| 文件大小: | 176K |

| 代理商: | MK2049-44SILF |

3.3V Communications Clock PLL

MDS 2049-44 A

5

Revision 050203

Integrated Circuit Systems, Inc. ● 525 Race Street, San Jose, CA 95126 ● tel (408) 295-9800 ●

www.icst.com

MK2049-44

As a general rule, the following relationship should be

maintained between components CS and CP in the loop

filter:

Charge Pump Current Table

Special considerations must be made in choosing loop

components CS and CP. These recommendations can

be found at

http://www.icst.com/products/telecom/loopfiltercap.htm

Series Termination Resistor

Clock output traces over one inch should use series

termination. To series terminate a 50

trace (a

commonly used trace impedance), place a 33

resistor

in series with the clock line, as close to the clock output

pin as possible. The nominal impedance of the clock

output is 20

. (The optional series termination resistor

is not shown in the External Component Schematic.)

Decoupling Capacitors

As with any high performance mixed-signal IC, the

MK2049-44 must be isolated from system power

supply noise to perform optimally.

Decoupling capacitors of 0.01F must be connected

between each VDD and the PCB ground plane. To

further guard against interfering system supply noise,

the MK2049-44 should use one common connection to

the PCB power plane as shown in the diagram on the

next page. The ferrite bead and bulk capacitor help

reduce lower frequency noise in the supply that can

lead to output clock phase modulation.

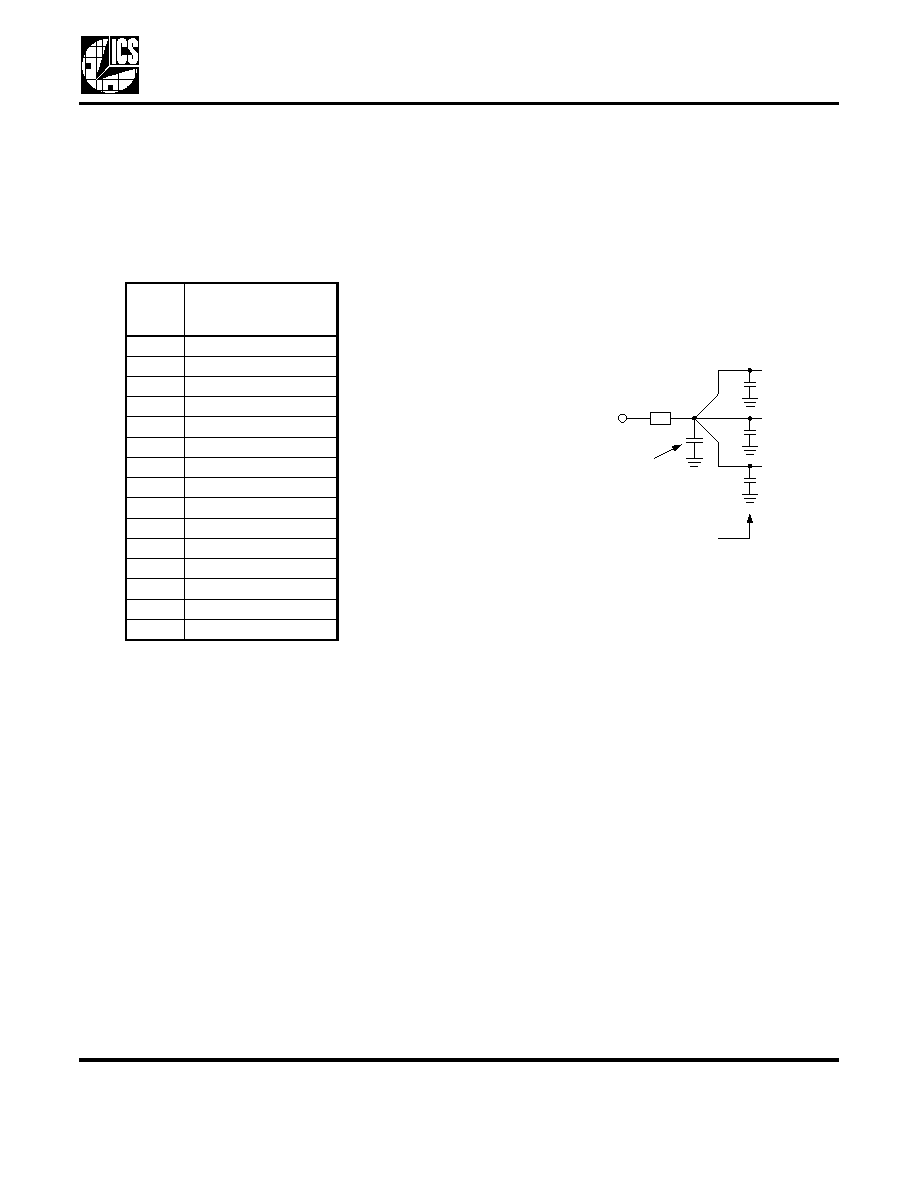

Recommended Power Supply Connection

for Optimal Device Performance

Crystal Load Capacitors

The device crystal connections should include pads for

small capacitors from X1 to ground and from X2 to

ground, shown as CL in the External Component

Schematic. These capacitors are used to adjust the

stray capacitance of the board to match the nominally

required crystal load capacitance. Because load

capacitance can only be increased in this trimming

process, it is important to keep stray capacitance to a

minimum by using very short PCB traces (and no via’s)

been the crystal and device.

In most cases the load capacitors will not be required.

They should not be stuffed on the prototype evaluation

board as the indiscriminate use of these trim capacitors

will typically cause more crystal centering error than

their absence. If the need for the load capacitors is later

determined, the values will fall within the 1-4 pF range.

The need for, and value of, these trim capacitors can

only be determined at prototype evaluation. Please

refer to MAN05 for the procedure to determine

capacitor values.

RSET

(k

)

Charge Pump Current

(ICP) (A)

13

174

15

150

16

139

18

121

20

106

22

95

24

85

27

74

36

52

47

38

56

30

75

21

100

15

150

10

200

7

C

P

C

S

20

------

≤

C onnec tion to 3.3V

Pow er Plane

Ferrite

B ead

B ulk D ec oupling C apac itor

(suc h as 1

F Tantalum )

VD D Pin

0.01

F D ecoupling C apacitors

相关PDF资料 |

PDF描述 |

|---|---|

| MK2049-45SITR | 125 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2049-45SILFTR | 125 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| MK2475-24SLFT | 60 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| MK2475-24ST | 60 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| MK2703BS | 27 MHz, OTHER CLOCK GENERATOR, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK2049-45 | 制造商:ICS 制造商全称:ICS 功能描述:3.3V Communications Clock PLL |

| MK2049-45ASI | 功能描述:IC CLK PLL COMM 3.3V 20-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| MK2049-45ASILF | 功能描述:时钟发生器及支持产品 3.3 VOLT COMMUNICA. CLOCK VCXO PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK2049-45ASILFTR | 功能描述:时钟发生器及支持产品 3.3 VOLT COMMUNICA. CLOCK VCXO PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK2049-45ASITR | 功能描述:IC CLK PLL COMM 3.3V 20-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。