- 您现在的位置:买卖IC网 > PDF目录45328 > MK2069-02GILF (INTEGRATED DEVICE TECHNOLOGY INC) 160 MHz, OTHER CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | MK2069-02GILF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 160 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| 封装: | 6.10 MM, 0.50 MM PITCH, TSSOP-56 |

| 文件页数: | 3/20页 |

| 文件大小: | 347K |

| 代理商: | MK2069-02GILF |

VCXO-Based Clock Jitter Attenuator and Translator

MDS 2069-02 G

11

Revision 050203

Integrated Circuit Systems, Inc. l 525 Race Street, San Jose, CA 95126 l tel (408) 295-9800 l

MK2069-02

Power Supply Considerations

As with any integrated clock device, the MK2069-02

has a special of set power supply requirements:

The feed from the system power supply must be

filtered for noise that can cause output clock jitter.

Power supply noise sources include the system

switching power supply or other system components.

The noise can interfere with device PLL components

such as the VCO or phase detector.

Each VDD pin must be decoupled individually to

prevent power supply noise generated by one device

circuit block from interfering with another circuit

block.

Clock noise from device VDD pins must not get onto

the PCB power plane or system EMI problems may

result.

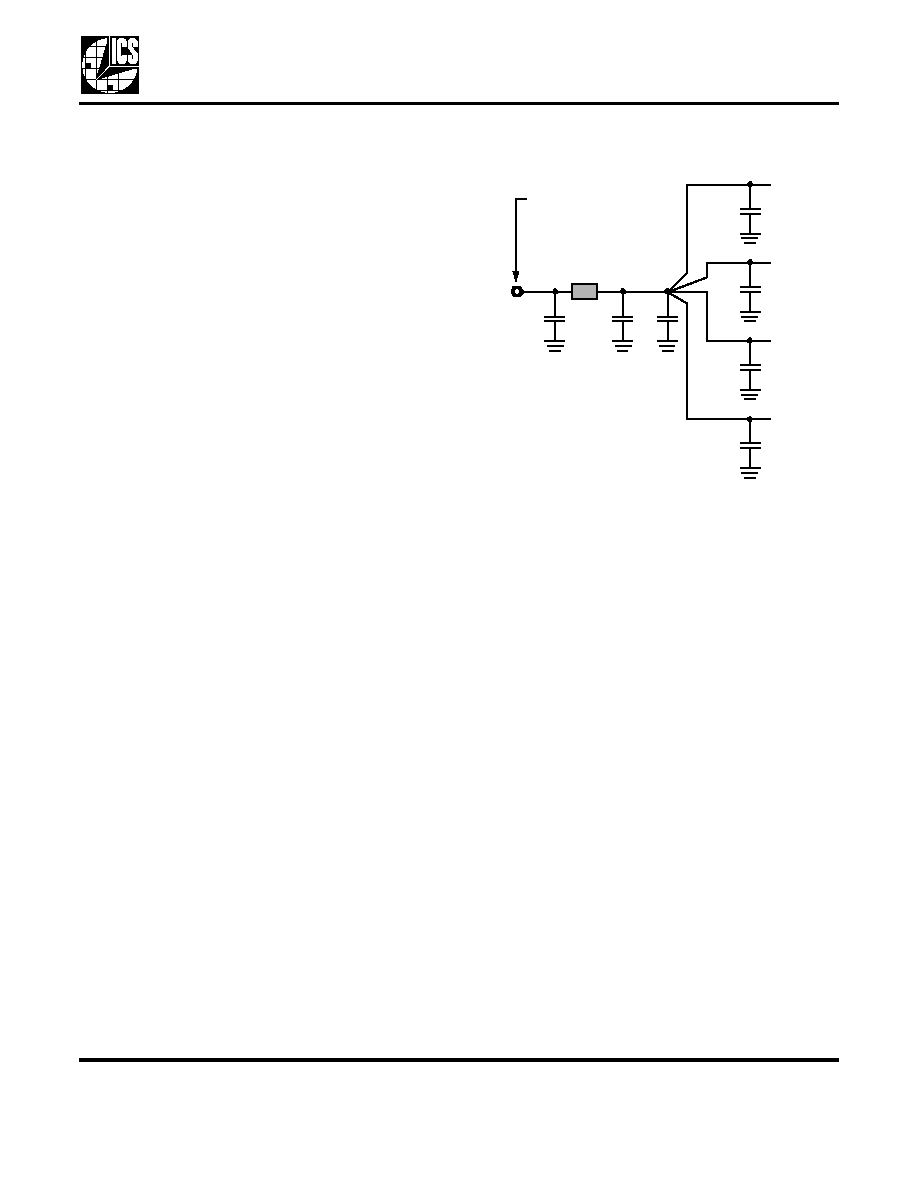

This above set of requirements is served by the circuit

illustrated in the Recommended Power Supply

Connection, below. The main features of this circuit are

as follows:

Only one connection is made to the PCB power

plane.

The capacitors and ferrite chip (or ferrite bead) on

the common device supply form a lowpass ‘pi’ filter

that remove noise from the power supply as well as

clock noise back toward the supply. The bulk

capacitor should be a tantalum type, 1

F minimum.

The other capacitors should be ceramic type.

The power supply traces to the individual VDD pins

should fan out at the common supply filter to reduce

interaction between the device circuit blocks.

The decoupling capacitors at the VDD pins should be

ceramic type and should be as close to the VDD pin

as possible. There should be no via’s between the

decoupling capacitor and the supply pin.

Recommended Power Supply Connection

Series Termination Resistor

Output clock PCB traces over 1 inch should use series

termination to maintain clock signal integrity and to

reduce EMI. To series terminate a 50

trace, which is a

commonly used PCB trace impedance, place a 33

resistor in series with the clock line as close to the clock

output pin as possible. The nominal impedance of the

clock output is 20

.

Quartz Crystal

The MK2069-02 operates by phase-locking the VCXO

circuit to the input signal at the selected ICLK input.

The VCXO consists of the external crystal and the

integrated VCXO oscillator circuit. To achieve the best

performance and reliability, a crystal device with the

recommended parameters must be used, and the

layout guidelines discussed in the following section

must be followed.

The frequency of oscillation of a quartz crystal is

determined by its cut and by the load capacitors

connected to it. The MK2069-02 incorporates variable

load capacitors on-chip which “pull” or change the

frequency of the crystal. The crystals specified for use

with the MK2069-02 are designed to have zero

frequency error when the total of on-chip + stray

C onnection Via to

3.3V Pow er Plane

F errite

Chip

0.

1

F

BU

L

K

1

n

F

VD D

Pin

0.

0

1

F

VD D

Pin

0.01

F

VD D

Pin

0.

0

1

F

VD D

Pin

0.

0

1

F

相关PDF资料 |

PDF描述 |

|---|---|

| MK2069-02GITR | 160 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| MK2069-02GILFTR | 160 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| MK2069-02GILFTR | 160 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| MK2069-03GITR | 160 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| MK2069-03GITR | 160 MHz, OTHER CLOCK GENERATOR, PDSO56 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK2069-03 | 制造商:ICS 制造商全称:ICS 功能描述:VCXO-Based Clock Translator with High Multiplication |

| MK2069-03GI | 功能描述:IC VCXO CLK TRANSLATOR 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:27 系列:Precision Edge® 类型:频率合成器 PLL:是 输入:PECL,晶体 输出:PECL 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/是 频率 - 最大:800MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 5.25 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC 包装:管件 |

| MK2069-03GITR | 功能描述:时钟发生器及支持产品 VCXO-BASED CLOCK TRANSLATOR RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK2069-04 | 制造商:ICS 制造商全称:ICS 功能描述:VCXO-Based Universal Clock Translator |

| MK2069-04GI | 功能描述:IC VCXO CLK TRANSLATOR 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。