- 您现在的位置:买卖IC网 > PDF目录45328 > MK2069-03GITR 160 MHz, OTHER CLOCK GENERATOR, PDSO56 PDF资料下载

参数资料

| 型号: | MK2069-03GITR |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 160 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| 封装: | 6.10 MM, 0.50 MM PITCH, TSSOP-56 |

| 文件页数: | 16/19页 |

| 文件大小: | 339K |

| 代理商: | MK2069-03GITR |

VCXO-Based Clock Translator with High Multiplication

MDS 2069-03

J

6

Revision 030906

Integrated Circuit Systems, Inc. l 525 Race Street, San Jose, CA 95126 l tel (408) 295-9800 l

MK2069-03

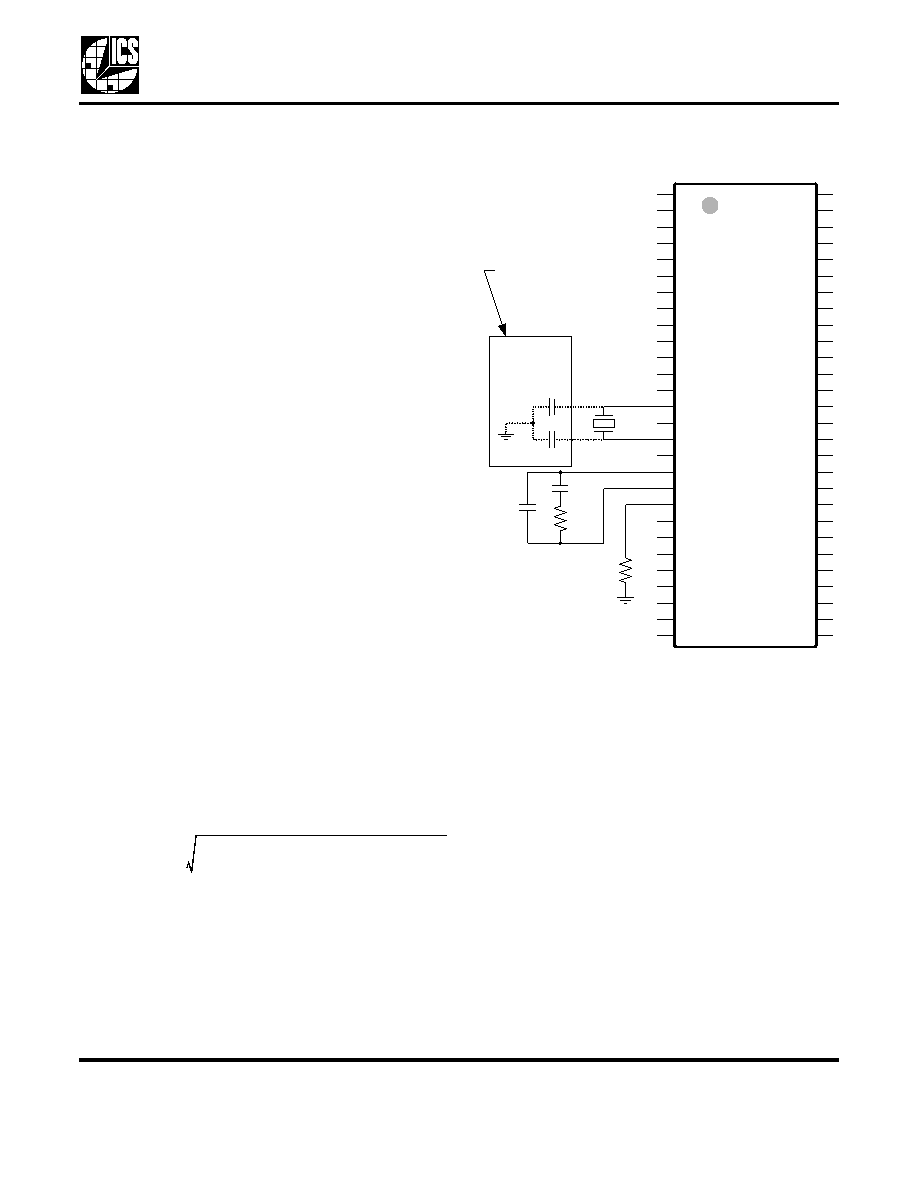

Setting the VCXO PLL Loop Response.

The VCXO PLL loop response is determined both by

fixed device characteristics and by variables set by the

user. This includes the values of RS, CS, CP and RSET

as shown in the External VCXO PLL Components

figure on this page.

The VCXO PLL loop bandwidth is approximated by:

Where:

RS = Value of resistor RS in loop filter in Ohms

ICP = Charge pump current in amps

(see table on page 7)

KO = VCXO Gain in Hz/V

(see table on page 8)

SV Divider = 1,2,4,6,8,10,12 or 16

FV Divider = 1 to 4096

The above equation calculates the “normalized” loop

bandwidth (denoted as “NBW”) which is approximately

equal to the - 3dB bandwidth. NBW does not take into

account the effects of damping factor or the second

pole imposed by CP. It does, however, provide a useful

approximation of filter performance.

To prevent jitter on VCLK due to modulation of the

VCXO PLL by the phase detector frequency, the

following general rule should be observed:

The PLL loop damping factor is determined by:

Where:

CS = Value of capacitor CS in loop filter in

Farads

External VCXO PLL Components

In general, the loop damping factor should be 0.7 or

greater to ensure output stability. A higher damping

factor will create less peaking in the passband and will

further assure output stability with the presence of

system and power supply noise. A damping factor of 4

will ensure a passband peak less then 0.2dB which

may be required for network clock wander transfer

compliance. A higher damping factor may also increase

output clock jitter when there is excess digital noise in

the system application, due to the reduced ability of the

PLL to respond to and therefore compensate for phase

noise ingress.

Notes on setting the value of CP

As another general rule, the following relationship

should be maintained between components CS and CP

in the loop filter:

NBW

RS ICP

×

K

O

×

2

π SV Divider

×

FV Divider

FPV Divider

×

-----------------------------------------------------------------------------------------------------------------

=

NBW(VCXO PLL)

f(Phase Detector)

20

---------------------------------------

≤

DF

RS

2

------

I

CP

CS

×

K

O

×

SV Divider

FV Divider

FPV Divider

×

----------------------------------------------------------------------------------------------------

×

=

R

SET

C

P

21

22

23

24

1

2

3

4

5

6

7

8

9

10

11

12

13

14

X1

15

16

X2

17

18

LFR

19

LF

20

ISET

25

26

27

28

36

35

34

33

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

32

31

30

29

M

K

2069

XTAL

C

L

C

L

R

S

C

S

Optional

Crystal Tuning

Capacitors

DON'T STUFF

Refer to "Crystal Tuning Load

Capacitors" Section

CP

CS

20

------

=

相关PDF资料 |

PDF描述 |

|---|---|

| MK2069-04GITR | 160 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| MK2069-04GI | 160 MHz, OTHER CLOCK GENERATOR, PDSO56 |

| MK20DN512ZVLL10 | RISC MICROCONTROLLER, PQFP100 |

| MK20DN512ZVLQ10 | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PQFP144 |

| MK20DX128ZVMD10 | 32-BIT, FLASH, 100 MHz, RISC MICROCONTROLLER, PBGA144 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MK2069-04 | 制造商:ICS 制造商全称:ICS 功能描述:VCXO-Based Universal Clock Translator |

| MK2069-04GI | 功能描述:IC VCXO CLK TRANSLATOR 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| MK2069-04GILF | 功能描述:时钟发生器及支持产品 VCXO-BASED UNIVERSAL CLOCK TRANSLATOR RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK2069-04GILFTR | 功能描述:时钟发生器及支持产品 VCXO-BASED UNIVERSAL CLOCK TRANSLATOR RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MK2069-04GITR | 功能描述:IC VCXO CLK TRANSLATOR 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。