- 您现在的位置:买卖IC网 > PDF目录80570 > MPC8535EAVTAQGA (FREESCALE SEMICONDUCTOR INC) 32-BIT, 1000 MHz, MICROPROCESSOR, PBGA783 PDF资料下载

参数资料

| 型号: | MPC8535EAVTAQGA |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 1000 MHz, MICROPROCESSOR, PBGA783 |

| 封装: | 29 X 29 MM, 2.80 MM HEIGHT, 1 MM PITCH, LEAD FREE, PLASTIC, FCBGA-783 |

| 文件页数: | 10/126页 |

| 文件大小: | 2861K |

| 代理商: | MPC8535EAVTAQGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页

Clocking

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 3

Freescale Semiconductor

107

2.23.2

CCB/SYSCLK PLL Ratio

The CCB clock is the clock that drives the e500 core complex bus (CCB), and is also called the platform clock. The frequency

of the CCB is set using the following reset signals, as shown in Table 75:

SYSCLK input signal

Binary value on LA[28:31] at power up

Note that there is no default for this PLL ratio; these signals must be pulled to the desired values.

2.23.3

e500 Core PLL Ratio

Table 76 describes the clock ratio between the e500 core complex bus (CCB) and the e500 core clock. This ratio is determined

by the binary value of LBCTL, LALE and LGPL2 at power up, as shown in Table 76.

2.23.4

DDR/DDRCLK PLL Ratio

The DDR memory controller complex can be synchronous with, or asynchronous to, the CCB, depending on configuration.

Table 77 describes the clock ratio between the DDR memory controller complex and the DDR/DDRCLK PLL reference clock,

DDRCLK, which is not the memory bus clock.

When synchronous mode is selected, the memory buses are clocked at half the CCB clock rate. The default mode of operation

is for the DDR data rate for the DDR controller to be equal to the CCB clock rate in synchronous mode, or the resulting DDR

PLL rate in asynchronous mode.

In asynchronous mode, the DDR PLL rate to DDRCLK ratios listed in Table 77 reflects the DDR data rate to DDRCLK ratio,

since the DDR PLL rate in asynchronous mode means the DDR data rate resulting from DDR PLL output.

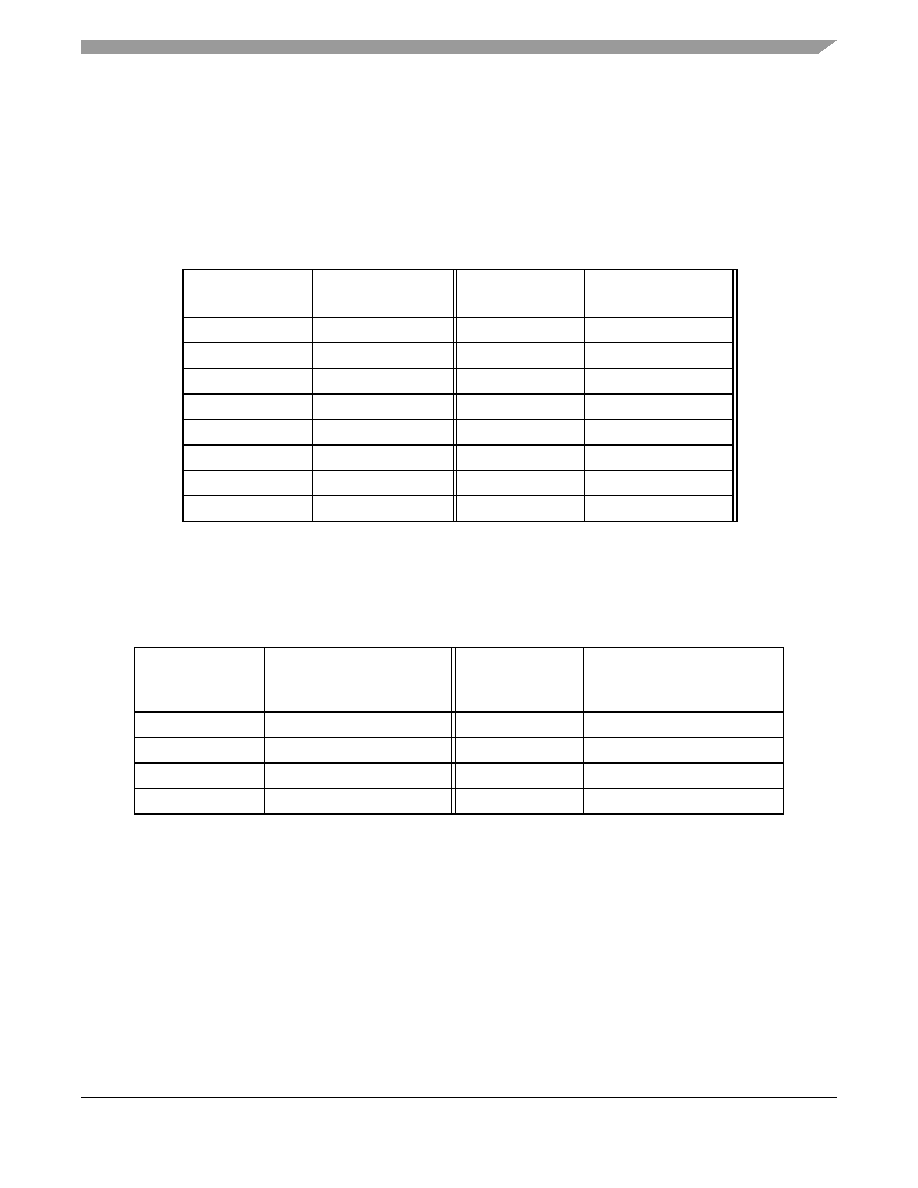

Table 75. CCB Clock Ratio

Binary Value of

LA[28:31] Signals

CCB:SYSCLK Ratio

Binary Value of

LA[28:31] Signals

CCB:SYSCLK Ratio

0000

Reserved

1000

8:1

0001

Reserved

1001

9:1

0010

Reserved

1010

10:1

0011

3:1

1011

Reserved

0100

4:1

1100

12:1

0101

5:1

1101

Reserved

0110

6:1

1110

Reserved

0111

Reserved

1111

Reserved

Table 76. e500 Core to CCB Clock Ratio

Binary Value of

LBCTL, LALE,

LGPL2 Signals

e500 core: CCB Clock Ratio

Binary Value of

LBCTL, LALE,

LGPL2 Signals

e500 core: CCB Clock Ratio

000

4:1

100

2:1

001

9:2

101

5:2

010

Reserved

110

3:1

011

3:2

111

7:2

相关PDF资料 |

PDF描述 |

|---|---|

| MPC8536EAVTANGA | 32-BIT, 800 MHz, MICROPROCESSOR, PBGA783 |

| MC9S08SG32E1WTLR | MICROCONTROLLER, PDSO28 |

| MUAC4K64-70TDI | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP100 |

| M30623M4-XXXGP | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP80 |

| M38513M4-XXXFP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO42 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC8535EAVTATH | 功能描述:微处理器 - MPU 8535E COMMERCIAL 1250 RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MPC8535EAVTATHA | 功能描述:微处理器 - MPU 8535 Encrypted RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MPC8535EAVTATLA | 功能描述:微处理器 - MPU 8535 ENCRYPTED RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MPC8535EBVTAKG | 功能描述:微处理器 - MPU 8535E INDUSTRIAL 600 RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MPC8535EBVTAKGA | 功能描述:微处理器 - MPU 8535 Encrypted RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

发布紧急采购,3分钟左右您将得到回复。