- 您现在的位置:买卖IC网 > Datasheet目录344 > MPC8569E-MDS-PB (Freescale Semiconductor)BOARD MOD DEV SYSTEM MPC8569 Datasheet资料下载

参数资料

| 型号: | MPC8569E-MDS-PB |

| 厂商: | Freescale Semiconductor |

| 文件页数: | 12/38页 |

| 文件大小: | 0K |

| 描述: | BOARD MOD DEV SYSTEM MPC8569 |

| 标准包装: | 1 |

| 系列: | PowerQUICC III™ |

| 类型: | MPU |

| 适用于相关产品: | MPC8569E |

| 所含物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

�� �

�

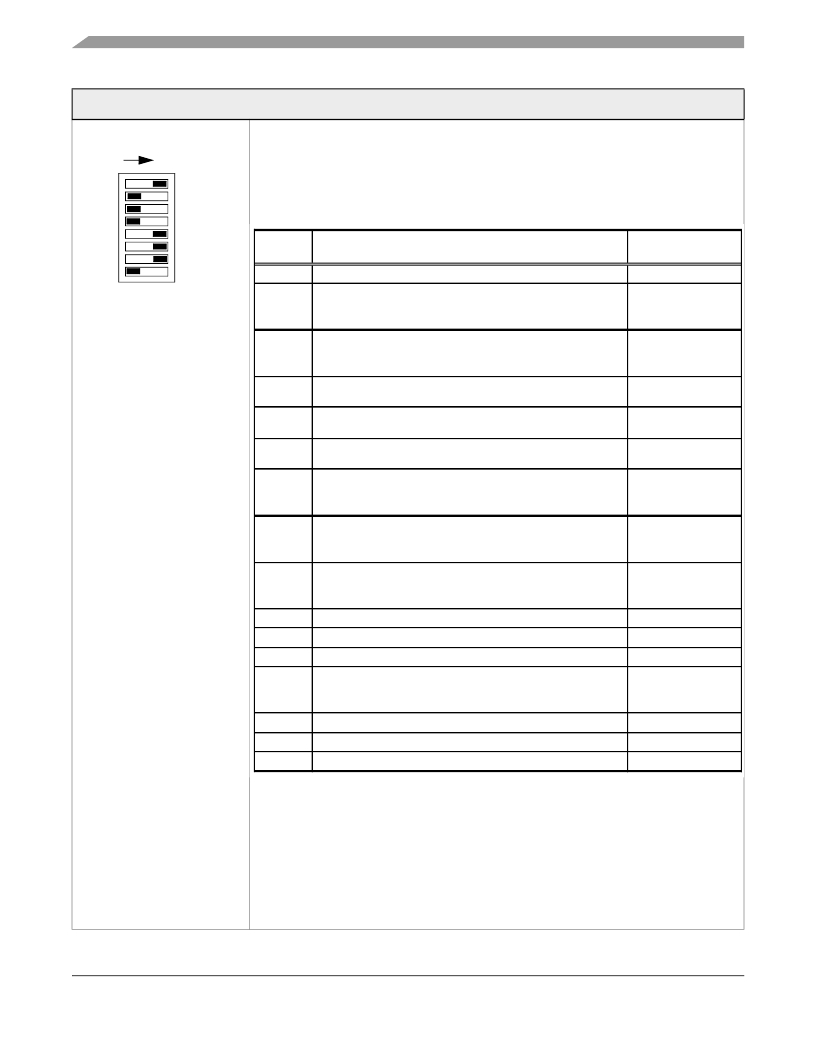

Switch� Default� Settings�

�SW8� Configuration:� I/O�

�NOTE!�

�ON� ’0’�

�100� MHz� clock� reference� (set� cfg_srds_refclk� to� 1).�

�125� MHz� clock� reference� (set� cfg_srds_refclk� to� 0).�

�1�

�2�

�PORT_SEL0�

�PORT_SEL1�

�3�

�4�

�PORT_SEL2�

�PORT_SEL3�

�SW8.1-SW8.4:� I/O� Port� Selection�

�5�

�6�

�7�

�8�

�RIO_ID5�

�RIO_ID6�

�RIO_ID7�

�RIO_SYS_SIZE�

�Value�

�(Binary)�

�0000�

�Description�

�-� PCI� Express� x1� (2.5� Gbps),� Lane� A�

�SerDes� Reference�

�Clock� Speed�

�100� MHz�

�-�

�SRIO1� 1x� (2.5� Gbps),� Lane� A�

�0001�

�0010�

�0011�

�0100�

�0101�

�0110�

�0111�

�(Default)�

�1000�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�-�

�SRIO2� 1x� (2.5� Gbps),� Lane� B�

�SGMII� x2� (1.25� Gbps;� half-speed),� Lanes� E–F�

�SRIO1� 1x� (2.5� Gbps;� half-speed),� Lane� A�

�SRIO2� 1x� (2.5� Gbps;� half-speed),� Lane� B�

�SGMII� x2� (1.25� Gbps;� half-speed),� Lanes� E–F�

�SRIO1� 1x� (3.125� Gbps),� Lane� A�

�SRIO2� 1x� (3.125� Gbps),� Lane� B�

�PCI� Express� x1� (2.5� Gbps),� Lane� A�

�SGMII� x2� (1.25� Gbps;� half-speed),� Lanes� E–F�

�PCI� Express� x2� (2.5� Gbps),� Lanes� A–B�

�SGMII� x2� (1.25� Gbps;� half-speed),� Lanes� E–F�

�PCI� Express� x1� (2.5� Gbps),� Lane� A�

�SRIO1� 1x� (2.5� Gbps),� Lane� E�

�SRIO2� 1x� (2.5� Gbps),� Lane� F�

�PCI� Express� x2� (2.5� Gbps),� Lanes� A–B�

�SRIO1� 1x� (2.5� Gbps),� Lane� E�

�SRIO2� 1x� (2.5� Gbps),� Lane� F�

�PCI� Express� x2� (2.5� Gbps),� Lanes� A–B�

�SRIO1� 1x� (2.5� Gbps� —half� speed),� Lane� E�

�SRIO2� 1x� (2.5� Gbps� —half� speed),� Lane� F�

�100� MHz�

�100� MHz�

�125� MHz�

�100� MHz�

�100� MHz�

�100� MHz�

�100� MHz�

�100� MHz�

�1001�

�1010�

�1011�

�1100�

�1101�

�1110�

�1111�

�-� SRIO1� 4x� (1.25� Gbps;� half-speed),� Lanes� A� –B,� E–F�

�-� SRIO1� 4x� (2.5� Gbps),� Lanes� A� –B,� E� –F�

�-� SRIO1� 4x� (3.125� Gbps),� Lanes� A� –B,� E� –F�

�-� PCI� Express� x1� (2.5� Gbps),� Lane� A�

�-� SRIO2� x1� (2.5� Gbps;� half-speed),� Lane� B�

�-� SGMII� x2� (1.25� Gbps;� half-speed),� Lanes� E–F�

�-� Serdes� disabled;� Lanes� A-B,� E-F� are� powered-off�

�-� Reserved�

�-� PCI� Express� x4� (2.5� Gbps),� Lanes� A–B,� E–F�

�100� MHz�

�100� MHz�

�125� MHz�

�100� MHz�

�-�

�-�

�100� MHz�

�SW8.5-SW8.7:� RapidIO� Device� ID� of� the� MPC8569E�

�?� Specifies� lower-order� bits� (3)� for� use� by� hosts� on� the� RapidIO� interface.�

�?� (Default)� If� configured� as� a� RapidIO� host� then� the� upper-order� device� ID� bits� default� to� ‘0’.�

�?� If� configured� as� a� RapidIO� agent� then� the� upper-order� device� ID� bits� default� to� ‘1’.�

�?� Regardless� of� host/agent� mode� configuration,� unconnected� cfg_device_ID_1[� n� ]� inputs�

�default� to� ‘1’.�

�SW8.8:� RapidIO� System� Size�

�?� ‘0’:� Large� system� size� with� a� maximum� of� 65,536� devices.�

�?� ‘1’:� (Default)� Small� system� size� with� a� maximum� of� 256� devices.�

�MPC8569E-MDS-PB� Hardware� Getting� Started,� Rev.� 3.1�

�12�

�Freescale� Semiconductor�

�相关PDF资料 |

PDF描述 |

|---|---|

| MPC8572EAMC | MPC8572 AMC RAPID SYSTEM |

| MPQ-ARM | ISP 4PORT FOR ARM CORTEX MCU |

| MP | SURGE SUPPRESSR 2/RJ11 MODEM/FAX |

| MR0A08BCYS35 | IC MRAM 1MBIT 35NS 44TSOP |

| MR0D08BMA45R | IC MRAM 1MBIT 45NS 48BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC8569EVTANKGB | 功能描述:数字信号处理器和控制器 - DSP, DSC 8569 800MHz rev2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| MPC8569EVTAQLJB | 功能描述:数字信号处理器和控制器 - DSP, DSC 8569 1GHz rev2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| MPC8569EVTAUNLB | 功能描述:数字信号处理器和控制器 - DSP, DSC 8569 1.33GHz rev2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| MPC8569VJAUNLB | 制造商:Freescale Semiconductor 功能描述:IC MPU PWRQUICC 1333MHZ 783FCBGA |

| MPC8569VTANKGB | 功能描述:数字信号处理器和控制器 - DSP, DSC 8569 ST 800/600/400 r2.1 RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。