- 您现在的位置:买卖IC网 > PDF目录2014 > MPC93H52AC (IDT, Integrated Device Technology Inc)IC CLK GEN ZD 1:11 32-LQFP PDF资料下载

参数资料

| 型号: | MPC93H52AC |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 12/14页 |

| 文件大小: | 0K |

| 描述: | IC CLK GEN ZD 1:11 32-LQFP |

| 标准包装: | 250 |

| 类型: | PLL 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS |

| 输出: | LVCMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:11 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 240MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-LQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 托盘 |

MPC93H52 REVISION 5 FEBRUARY 15, 2013

7

2013 Integrated Device Technology, Inc.

MPC93H52 Data Sheet

3.3 V 1:11 LVCMOS ZERO DELAY CLOCK GENERATOR

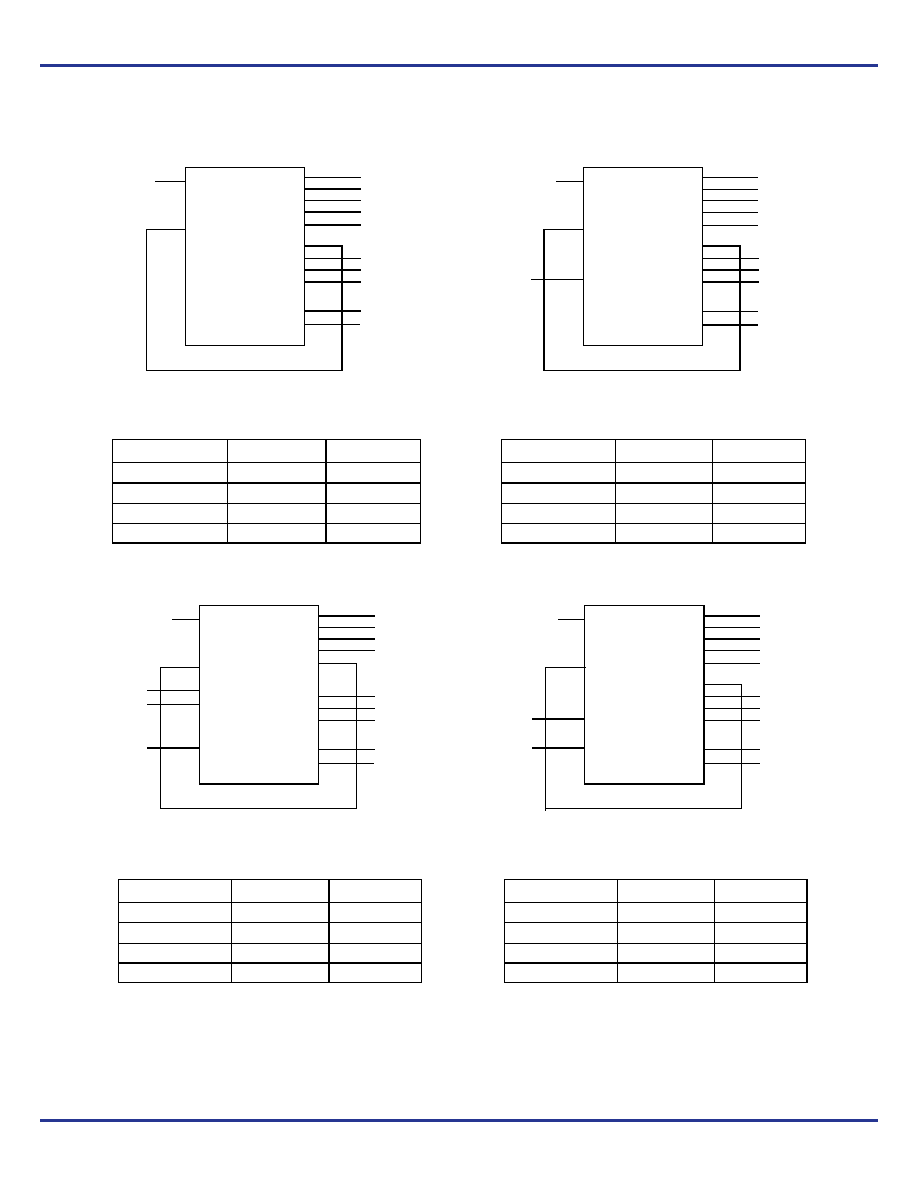

Example Configurations for the MPC93H52

Figure 3. MPC93H52 Default Configuration

Figure 4. MPC93H52 Default Configuration

Figure 5. MPC93H52 Default Configuration

Figure 6. MPC93H52 Default Configuration

F_RANGE

MPC93H52

fref = 100 MHz

100 MHz

100 MHz (Feedback)

200 MHz

CCLK

FB_IN

FSELA

FSELB

FSELD

QA0

QA1

QA2

QA3

QB0

QB1

QB2

QB3

QC0

QC1

QA4

MPC93H52 default configuration (feedback of QB0 =

100 MHz). All control pins are left open.

Frequency range

Min

Max

Input

50 MHz

120 MHz

QA outputs

50 MHz

120 MHz

QB outputs

50 MHz

120 MHz

QC outputs

100 MHz

240 MHz

F_RANGE

MPC93H52

fref = 62.5 MHz

62.5 MHz

62.5 MHz (Feedback)

62.5 MHz

MPC93H52 zero-delay (feedback of QB0 = 62.5 MHz). All

control pins are left open except FSELC = 1. All outputs are

locked in frequency and phase to the input clock.

CCLK

FB_IN

FSELA

FSELB

FSELC

QA0

QA1

QA2

QA3

QB0

QB1

QB2

QB3

QC0

QC1

QA4

VCC

Frequency range

Min

Max

Input

50 MHz

120 MHz

QA outputs

50 MHz

120 MHz

QB outputs

50 MHz

120 MHz

QC outputs

50 MHz

120 MHz

F_RANGE

Frequency range

Min

Max

Input

25 MHz

60 MHz

QA outputs

50 MHz

120 MHz

QB outputs

50 MHz

120 MHz

QC outputs

100 MHz

240 MHz

MPC93H52

fref = 33.3 MHz

33.3 MHz

50 MHz

33.3 MHz (Feedback)

100 MHz

MPC93H52 configuration to multiply the reference frequen-

cy by 3, 3

2 and 1. PLL feedback of QA4 = 33.3 MHz.

CCLK

FB_IN

FSELA

FSELB

FSELC

QA0

QA1

QA2

QA3

QB0

QB1

QB2

QB3

QC0

QC1

QA4

VCC

F_RANGE

Frequency range

Min

Max

Input

25 MHz

60 MHz

QA outputs

25 MHz

60 MHz

QB outputs

25 MHz

60 MHz

QC outputs

25 MHz

60 MHz

MPC93H52

fref = 33.3 MHz

33.3 MHz

33.3 MHz (Feedback)

33.3 MHz

MPC93H52 zero-delay (feedback of QB0 = 33.3 MHz).

Equivalent to Table 2. except F_RANGE = 1 enabling a

lower input and output clock frequency.

CCLK

FB_IN

FSELA

FSELB

FSELC

QA0

QA1

QA2

QA3

QB0

QB1

QB2

QB3

QC0

QC1

QA4

VCC

相关PDF资料 |

PDF描述 |

|---|---|

| MPC93R51AC | IC PLL CLK DRIVER LV 32-LQFP |

| MPC9608AC | IC CLOCK BUFFER ZD 1:10 32-LQFP |

| MPC962309EJ-1H | IC BUFFER ZD 1:5 3.3V 16-TSSOP |

| MPC96877VK | IC CLK DRIVER 1:10 SDRAM 52-BGA |

| MPC9773AE | IC PLL CLK GEN 1:12 3.3V 52-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC93H52ACR2 | 功能描述:IC CLK GEN ZD 1:11 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| MPC93H52FA | 功能描述:IC CLOCK GEN/DVR HI-DRIVE 32LQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| MPC93H52FAR2 | 制造商:Integrated Device Technology Inc 功能描述:ZERO DLY PLL CLOCK GEN SGL 32LQFP - Tape and Reel |

| MPC93R51 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:LOW VOLTAGE PLL CLOCK DRIVER |

| MPC93R51AC | 功能描述:时钟驱动器及分配 3.3V 240MHz Clock Generator RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。