- 您现在的位置:买卖IC网 > PDF目录2099 > MPC9658AC (IDT, Integrated Device Technology Inc)IC PLL CLK GEN 1:10 3.3V 32-LQFP PDF资料下载

参数资料

| 型号: | MPC9658AC |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 10/12页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLK GEN 1:10 3.3V 32-LQFP |

| 标准包装: | 250 |

| 类型: | PLL 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | LVPECL |

| 输出: | LVCMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:10 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 250MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-LQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 托盘 |

MPC9658 REVISION 6 JANUARY 8, 2013

7

2013 Integrated Device Technology, Inc.

MPC9658 Data Sheet

3.3V 1:10 LVCMOS PLL CLOCK GENERATOR

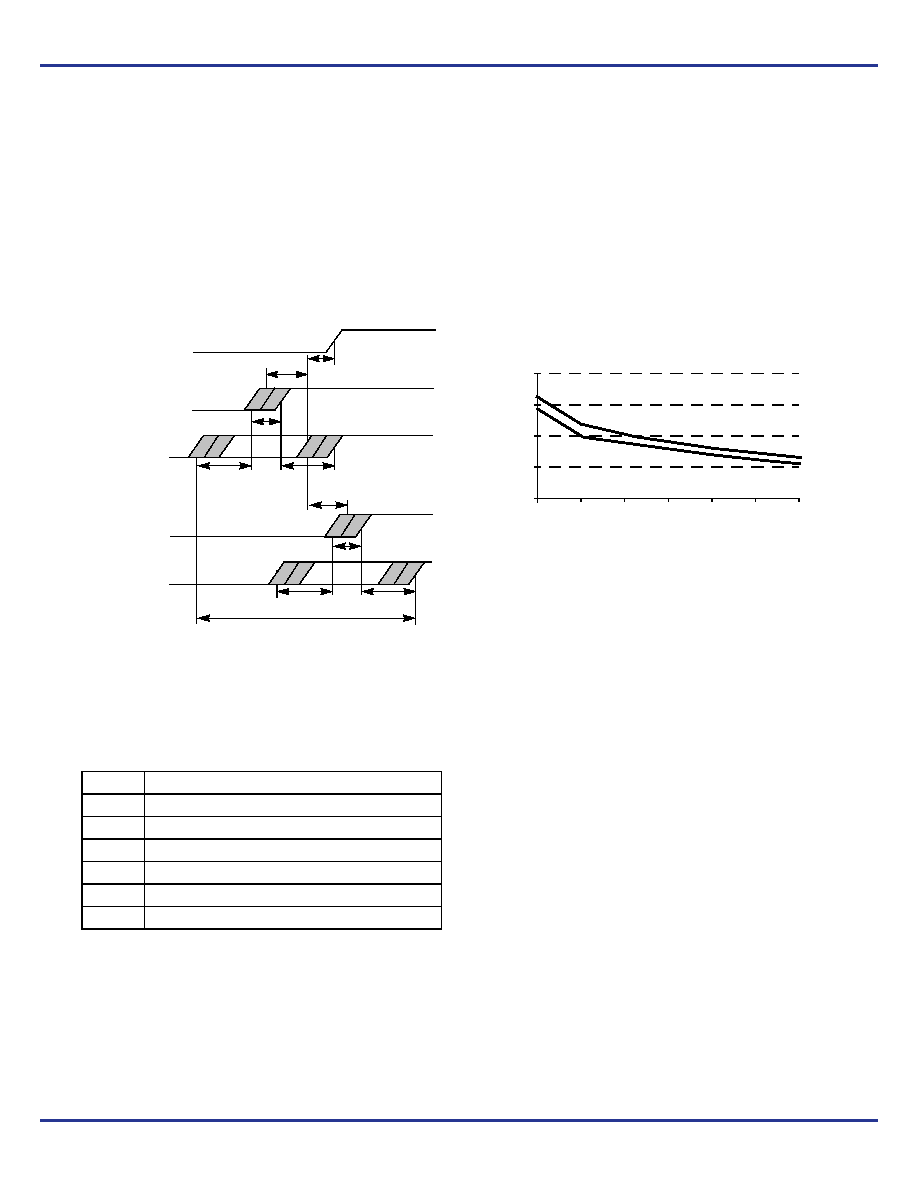

Calculation of Part-to-Part Skew

The MPC9658 zero delay buffer supports applications

where critical clock signal timing can be maintained across

several devices. If the reference clock inputs of two or more

MPC9658 are connected together, the maximum overall

timing uncertainty from the common PCLK input to any output

is:

tSK(PP) = t() + tSK(O) + tPD, LINE(FB) + tJIT() CF

This maximum timing uncertainty consist of four

components: static phase offset, output skew, feedback

board trace delay, and I/O (phase) jitter:

Figure 4. MPC9658 Max. Device-to-Device Skew

Due to the statistical nature of I/O jitter a RMS value (1

)

is specified. I/O jitter numbers for other confidence factors

(CF) can be derived from Table 8.

The feedback trace delay is determined by the board

layout and can be used to fine-tune the effective delay

through each device. In the following example calculation a

I/O jitter confidence factor of 99.7% (

3) is assumed,

resulting in a worst case timing uncertainty from input to any

output of –214 ps to 224 ps relative to PCKL (fREF = 100 MHz,

FB = 4, tjit() = 8 ps RMS at fVCO = 400 MHz):

tSK(PP) = [–70ps...80ps] + [–120ps...120ps] +

[(8ps

–3)...(8ps 3)] + tPD, LINE(FB)

tSK(PP) = [–214ps...224ps] + tPD, LINE(FB)

Due to the frequency dependence of the I/O jitter, Figure 5

can be used for a more precise timing performance analysis.

Figure 5. Max. I/O Jitter versus Frequency

Driving Transmission Lines

The MPC9658 clock driver was designed to drive high

speed signals in a terminated transmission line environment.

To provide the optimum flexibility to the user, the output

drivers were designed to exhibit the lowest impedance

possible. With an output impedance of less than 20

the

drivers can drive either parallel or series terminated

transmission lines. For more information on transmission

lines, the reader is referred to Freescale Semiconductor

Application Note AN1091. In most high performance clock

networks, point-to-point distribution of signals is the method

of choice. In a point-to-point scheme, either series terminated

or parallel terminated transmission lines can be used. The

parallel technique terminates the signal at the end of the line

with a 50

resistance to VCC 2.

This technique draws a fairly high level of DC current and

thus only a single terminated line can be driven by each

output of the MPC9658 clock driver. However, for the series

terminated case there is no DC current draw, thus the

outputs can drive multiple series terminated lines. Figure 6

illustrates an output driving a single series terminated line

versus two series terminated lines in parallel. When taken to

its extreme, the fanout of the MPC9658 clock driver is

effectively doubled due to its capability to drive multiple lines.

Table 8. Confidence Factor CF

CF

Probability of clock edge within the distribution

1

0.68268948

2

0.95449988

3

0.99730007

4

0.99993663

5

0.99999943

6

0.99999999

tPD,LINE(FB)

tJIT()

+tSK(O)

—t()

+t()

tJIT()

+tSK(O)

tSK(PP)

Max. skew

TCLKCommon

QFBDevice 1

Any QDevice 1

QFBDevice2

Any QDevice 2

FCO Frequency [MHz]

200

250

300

350

400

450

500

FB = 4

FB = 2

0

15

10

5

20

t jit

(f)

[ps

]RMS

I/O Phase Jitter versus Frequency

Parameter: PLL Feedback Divider FB

相关PDF资料 |

PDF描述 |

|---|---|

| MPC9772FA | IC PLL CLK GEN 1:12 3.3V 52-LQFP |

| MPC9774FAR2 | IC PLL CLK GEN 1:14 3.3V 52-LQFP |

| MPC97H74AE | IC PLL CLK GEN 1:14 3.3V 52-LQFP |

| MPC9993AC | IC PLL CLK DRIVER IDCS 32-LQFP |

| MPC99J93AC | IC PLL CLK DRIVER IDCS 32-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC9658ACR2 | 功能描述:时钟发生器及支持产品 FSL 1-10 LVCMOS Zero Delay Buffer RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9658FA | 功能描述:时钟发生器及支持产品 2.5 3.3V 250MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9658FAR2 | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 32-Pin LQFP T/R 制造商:Integrated Device Technology Inc 功能描述:MPC9658FAR2 - Tape and Reel |

| MPC96877VK | 功能描述:时钟发生器及支持产品 DDR2 PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC96877VKR2 | 功能描述:时钟发生器及支持产品 DDR2 PLL RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。